Fakultät II – Informatik, Wirtschafts- und Rechtswissenschaften Department für Informatik

# Ein Ansatz für die Nutzung teildefekter Field Programmable Gate Arrays (FPGAs) in der Serienproduktion

Dissertation zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften

von

Dipl.-Inform. Sven Frimont

#### Gutachter:

Prof. Dr. Wolfgang Nebel Prof. Dr. Achim Rettberg

Tag der Disputation: 13. Oktober 2009

## **Danksagung**

Meinem Referenten, Herrn Prof. Nebel, danke ich für die wissenschaftliche Betreuung der Arbeit und seine wertvollen Anregungen. Insbesondere danke ich ihm für die Gewährung von zeitlichen Freiräumen während der Erstellung der Dissertation. Herrn Prof. Rettberg danke ich für sein Interesse an der Arbeit und die Übernahme des Korreferates.

Bedanken möchte ich mich auch bei den stets an einer Zusammenarbeit interessierten Kollegen aus meiner Arbeitsgruppe an der Universität und am OFFIS, dem "Oldenburger Forschungs- und Entwicklungsinstitut für Informatikwerkzeuge und -systeme". Insbesondere Andreas Schallenberg, Frank Oppenheimer und Henrik Lipskoch haben durch Anregungen in zahlreichen Diskussionen wesentlich zum Gelingen dieser Arbeit beigetragen.

# **Inhaltsverzeichnis**

| 1 | Einl | Einleitung 1                                                    |  |  |  |  |  |

|---|------|-----------------------------------------------------------------|--|--|--|--|--|

|   | 1.1  | Motivation                                                      |  |  |  |  |  |

|   | 1.2  | Stand der Technik                                               |  |  |  |  |  |

|   | 1.3  | Wesentliche Beiträge der Arbeit                                 |  |  |  |  |  |

|   | 1.4  | Inhaltsübersicht                                                |  |  |  |  |  |

| 2 | Gru  | ndlagen 7                                                       |  |  |  |  |  |

|   | 2.1  | Aufbau eines FPGAs                                              |  |  |  |  |  |

|   |      | 2.1.1 Aufbau eines Logikblocks                                  |  |  |  |  |  |

|   |      | 2.1.2 Programmierbare Verbindungsleitungen                      |  |  |  |  |  |

|   | 2.2  | Rechnergestützter Schaltungsentwurf für FPGAs                   |  |  |  |  |  |

|   |      | 2.2.1 Allgemeiner Entwurfsablauf                                |  |  |  |  |  |

|   |      | 2.2.2 IP-basierter Entwurf                                      |  |  |  |  |  |

|   |      | 2.2.3 Timing-Analyse                                            |  |  |  |  |  |

|   | 2.3  | Die Ausbeute bei der Herstellung von FPGAs                      |  |  |  |  |  |

| 3 | Test | und Diagnose von FPGAs 29                                       |  |  |  |  |  |

|   | 3.1  | Fehlermodelle                                                   |  |  |  |  |  |

|   | 3.2  | Diagnose über FPGA-BIST                                         |  |  |  |  |  |

|   | 3.3  | Erstellung und Bereitstellung einer Defect Map                  |  |  |  |  |  |

|   | 3.4  | Zusammenfassung                                                 |  |  |  |  |  |

| 4 | Verd | gleichbare Arbeiten 39                                          |  |  |  |  |  |

| • | 4.1  | Passive Verfahren                                               |  |  |  |  |  |

|   | 4.2  | Einfügen von redundanten Komponenten in die FPGA-Architektur 41 |  |  |  |  |  |

|   |      | 4.2.1 Redundante Zeilen und/oder Spalten                        |  |  |  |  |  |

|   |      | 4.2.2 Redundante Logikblöcke                                    |  |  |  |  |  |

|   | 4.3  | Veränderung der Programmierung des FPGAs                        |  |  |  |  |  |

|   | 1.5  | 4.3.1 Individuelle Konfiguration für jedes FPGA                 |  |  |  |  |  |

|   |      | 4.3.2 Dynamisches Place & Route                                 |  |  |  |  |  |

|   |      | 4.3.3 Anpassung der Konfiguration                               |  |  |  |  |  |

|   |      | 4.3.4 Prekompilierte Schaltungsteile                            |  |  |  |  |  |

|   | 4.4  | Zusammenfassung 55                                              |  |  |  |  |  |

| 5                   | ore basierter Ansatz | 57       |                                                         |       |  |  |

|---------------------|----------------------|----------|---------------------------------------------------------|-------|--|--|

|                     | 5.1                  | n-Flow   |                                                         |       |  |  |

|                     | 5.2                  |          | stellung einer Hard-Core-Version                        |       |  |  |

|                     |                      |          | Generierung der Varianten                               |       |  |  |

|                     |                      | 5.2.2    | Zeitverhalten einer Hard-Core-Version                   |       |  |  |

|                     |                      | 5.2.3    | Funktionswahrscheinlichkeit einer Hard-Core-Version     |       |  |  |

|                     | 5.3                  |          | führung des Re-Mapping                                  |       |  |  |

|                     |                      | 5.3.1    | Funktionswahrscheinlichkeit einer DT-Konfiguration      |       |  |  |

|                     |                      | 5.3.2    | Zeitverhalten einer DT-Konfiguration                    |       |  |  |

|                     |                      | 5.3.3    | Ein Re-Mapping-Algorithmus                              |       |  |  |

|                     | 5.4                  | _        | mmierung teildefekter FPGAs in der Serienproduktion     |       |  |  |

|                     | 5.5                  | Zusam    | menfassung                                              | . 118 |  |  |

| 6                   | Bew                  | ertung   | des Ansatzes                                            | 121   |  |  |

|                     | 6.1                  | Verbes   | serung der Ausbeute                                     | . 121 |  |  |

|                     | 6.2                  | Reduz    | ierung der Kosten für die Massenproduktion              | . 124 |  |  |

|                     |                      | 6.2.1    | Eine Vorhersage des nutzbaren Anteils an defekten FPGAs | . 125 |  |  |

|                     |                      | 6.2.2    | Einsparungen durch die Nutzung von defekten FPGAs       | . 128 |  |  |

|                     | 6.3                  | Vergle   | ich mit anderen Arbeiten                                | . 131 |  |  |

|                     |                      | 6.3.1    | Defect Coverage                                         | . 132 |  |  |

|                     |                      | 6.3.2    | Area Overhead                                           | . 134 |  |  |

|                     |                      | 6.3.3    | Timing Overhead                                         | . 135 |  |  |

|                     |                      | 6.3.4    | Bitfile size                                            | . 136 |  |  |

|                     |                      | 6.3.5    | Extra HW required                                       | . 136 |  |  |

|                     |                      | 6.3.6    | Maturity                                                | . 137 |  |  |

|                     |                      | 6.3.7    | Mass production friendly                                | . 138 |  |  |

|                     |                      | 6.3.8    | Timing-closure friendly                                 | . 138 |  |  |

|                     |                      | 6.3.9    | Reconfigurability                                       |       |  |  |

|                     | 6.4                  | Zusam    | menfassung                                              |       |  |  |

| 7                   | Zus                  | ammen    | fassung                                                 | 145   |  |  |

| ۸ <b>۱</b>          | hild:                | ingeve:  | rzeichnis                                               | 150   |  |  |

| ΑÜ                  | וטווענ               | iiigsvei | ZCICIIIIS                                               | 150   |  |  |

| Tabellenverzeichnis |                      |          |                                                         |       |  |  |

| Lit                 | Literaturverzeichnis |          |                                                         |       |  |  |

## 1 Einleitung

Dieses Kapitel führt den Leser in die Thematik ein und gibt einen Überblick über die wesentlichen Ziele und Inhalte der vorliegenden Arbeit.

## 1.1 Motivation

Digitale logische Schaltungen findet man heutzutage in fast jedem elektronischen Produkt. Je nach produzierter Stückzahl werden diese Schaltungen unterschiedlich realisiert. Bei einer Herstellung des Produktes in sehr hohen Stückzahlen kann gegenüber einer Realisierung aus den bereits am Markt erhältlichen Standardbausteinen eine Kostensenkung erreicht werden, indem die Schaltungen auf einen Chip integriert werden. Da der so entstehende Chip durch den Chip-Hersteller speziell für den vorgesehenen Verwendungszweck erstellt wird, spricht man hier von einer anwendungsspezifischen integrierten Schaltung (Application Specific Integrated Circuit – ASIC). Eine alternative Möglichkeit für die Realisierung der in einem Produkt benötigten Schaltungen bieten sogenannte FPGAs (Field Programmable Gate Arrays) als frei programmierbare ICs. Wenn die zu fertigenden Stückzahlen in einer Serienproduktion die hohen initialen Kosten für eine ASIC-Produktion nicht rechtfertigen, ist die Verwendung eines FPGAs für die Serienproduktion eine oft gewählte Alternative.

Die Fertigung von FPGAs in immer kleineren Strukturen verursacht - vor allem dann, wenn FPGAs erstmalig in einer neuen Prozessgeneration hergestellt werden - eine zunehmende Defektdichte bei der Herstellung. Da eine sinkende Ausbeute direkte Auswirkungen auf den Stückpreis eines FPGAs und seine Verfügbarkeit am Markt hat, nutzen die führenden FPGA-Hersteller Verfahren, die eine Steigerung der Ausbeute durch die Nutzung von defekten FPGAs ermöglichen.

#### 1.2 Stand der Technik

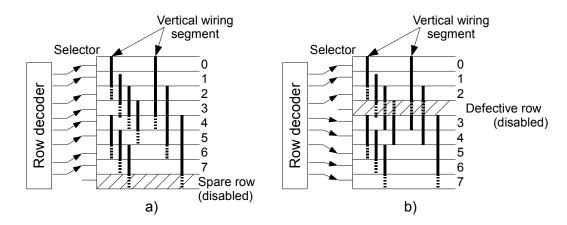

Eine spezielle Routing-Architektur, die lange Verbindungssegmente verwendet, ermöglicht dem FPGA-Hersteller Altera die Anwendung eines Verfahrens für die Nutzung

von defekten FPGAs, das auf redundant vorhandenen Spalten von Logikblöcken basiert. Defekte Logikblock-Spalten werden nach der FPGA-Herstellung durch redundant vorhandene Spalten ersetzt. Die Ansteuerung der Logikblöcke durch den Konfigurationsspeicher auf dem FPGA wird so verändert, dass die Programmierung des FPGAs wie gewohnt erfolgen kann. Altera konnte durch die Anwendung dieses Verfahrens bereits in einigen der angebotenen FPGA-Familien die Ausbeute an nutzbaren FPGAs steigern [alt00] und setzt auch in der aktuellen Herstellung der Stratix IV-FPGAs ein Verfahren ein, das mit redundanten Schaltungen arbeitet [alt08]. Dieses Verfahren kann bei FPGAs, deren Architektur viele kurze Verbindungssegmente enthalten (*island-style* und *row-based* FPGAs, siehe Abschnitt 2.1.2), nur mit einer aufwändigen Erweiterung der Verbindungsstrukturen eingesetzt werden.

Der FPGA-Hersteller Xilinx wendet für seine im *island-style* konstruierten FPGAs ein Verfahren an, das nicht auf eine Veränderung der bestehenden FPGA-Architektur angewiesen ist und zudem keine Lokalisierung der Defekte auf dem FPGA erfordert¹. Leicht defekte FPGAs werden erneut getestet, wobei ein spezieller Test durchgeführt wird, bei dem nur die von dem Kunden tatsächlich genutzten Teile des FPGAs getestet werden. Wenn die FPGAs diesen Test erfolgreich durchlaufen, werden sie dem Kunden für eine Serienproduktion verkauft. Ein Nachteil dieser Vorgehensweise ist der Verlust der Rekonfigurierbarkeit der FPGAs. Die defekten FPGAs können nur mit FPGA-Konfigurationen verwendet werden, mit denen sie vorher bei dem FPGA-Hersteller getestet wurden. Wenn später während der Produktion eine Nachbesserung des Designs erforderlich ist, können die bereits mit der FPGA-Konfiguration getesteten und erworbenen FPGAs nicht mehr verwendet werden. Ein nachträgliches Update einer FPGA-Konfiguration nach der Auslieferung des Produktes an den Kunden ist ebenfalls nicht mehr möglich.

## 1.3 Wesentliche Beiträge der Arbeit

Der Einsatz der oben vorgestellten Verfahren bei den führenden FPGA-Herstellern zeigt, dass die Steigerung der Ausbeute durch die Verwendung von defekt hergestellten FPGAs von zunehmender Bedeutung ist. Das von dem FPGA-Hersteller Altera verwendete Verfahren kann jedoch nicht für alle FPGA-Architekturen problemlos verwendet werden. Auch das von Xilinx genutzte Verfahren ist nicht unproblematisch aufgrund der eingeschränkten Rekonfigurierbarkeit des FPGAs.

Alternativ zu der Anpassung eines FPGAs an die vorliegende FPGA-Konfiguration besteht eine naheliegende Möglichkeit für die Nutzung von teildefekten FPGAs darin, die bei der Programmierung vorhandene Flexibilität auszunutzen. Da FPGAs aus vielen

<sup>&</sup>lt;sup>1</sup>Easy Path FPGA Series [eas08]

gleich aufgebauten Schaltungselementen bestehen, kann die Konfiguration eines FPGAs derart erfolgen, dass die defekten Schaltungselemente des FPGAs nicht verwendet werden. Die Eignung dieses Ansatzes für eine Serienproduktion hängt von der Zeit (und damit den Kosten) ab, die für die Durchführung der folgenden Schritte benötigt wird:

- 1. Lokalisierung der defekten Schaltungsteile auf dem FPGA

- 2. Erstellung einer individuellen FPGA-Konfiguration unter Umgehung der Defekte

Für den in der vorliegenden Arbeit entwickelten Ansatz ist eine Lokalisierung der defekten Logikblöcke, also eine Diagnose der defekt produzierten FPGAs, eine unabdingbare Voraussetzung. Da in dem Ansatz defekte Logikblöcke umgangen werden, müssen diese zuvor in einer Diagnose des FPGAs identifiziert werden. Forschungen zu alternativen Diagnose-Verfahren zielen darauf ab, die momentan sehr hohen Kosten für eine Diagnose eines FPGAs zu reduzieren. Aufgrund der technologischen Entwicklung wird allgemein vermutet, dass zukünftige FPGA-Generationen deutlich mehr Defekte enthalten, als die zur Zeit produzierten FPGAs. Sinkende Kosten auf der Seite der Diagnose-Verfahren und steigende Kosten aufgrund einer sinkenden Ausbeute an FPGAs könnten so in Zukunft zu wirtschaftlich einsetzbaren Diagnose-Verfahren führen. Das Problem einer effizienten Lokalisierung von defekten Schaltungsteilen auf einem FPGA wird durch den in dieser Arbeit entwickelten Ansatz nicht behandelt. Die Position der defekten Logikblöcke innerhalb des FPGAs wird als bekannt vorausgesetzt.

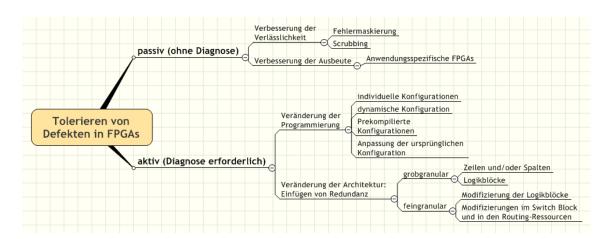

Da die Programmierung von teildefekten FPGAs innerhalb einer Serienproduktion ein zeitkritischer Faktor ist, kann die Platzierung und Verdrahtung der Schaltung nicht für jedes FPGA individuell erfolgen, bevor das FPGA in der Produktion programmiert wird. Existierende Forschungsansätze, die eine beschleunigte Programmierung von teildefekten FPGAs in der Produktion ermöglichen, können wie folgt grob kategorisiert werden:

- Dynamische Platzierung und Verdrahtung auf dem FPGA

Die Platzierung und die Verdrahtung der Schaltung werden erst nach der Programmierung in der Produktion auf dem FPGA durchgeführt.

- Anpassung einer bestehenden Konfiguration des FPGAs unter Umgehung der Defekte

Eine flexible FPGA-Konfiguration wird jeweils mit einem geringen Zeitaufwand direkt vor oder direkt nach der Programmierung in der Produktion an das jeweils vorliegende defekte FPGA angepasst.

Der in der vorliegenden Arbeit entwickelte Ansatz kann der letztgenannten Kategorie zugeordnet werden. Eine besondere Herausforderung für Forschungsansätze in dieser Kategorie ist die Vorhersage des kritischen Pfades für die auf dem FPGA realisierte Schaltung, da sich die Anpassung der FPGA-Konfiguration an ein defektes FPGA auf die Verzögerungszeiten innerhalb dieser Schaltung auswirken kann. Da vorher nicht bekannt ist, welche Defekte auf den zu programmierenden FPGAs vorliegen, kann für

die Schaltung nur der längste Pfad, der aufgrund einer Anpassung an ein defektes FPGA entstehen kann, als obere Schranke für die Verzögerungszeit garantiert werden. Diese pessimistische obere Schranke für die Verzögerungszeit muss daher als kritischer Pfad für die realisierte Schaltung angesehen werden.

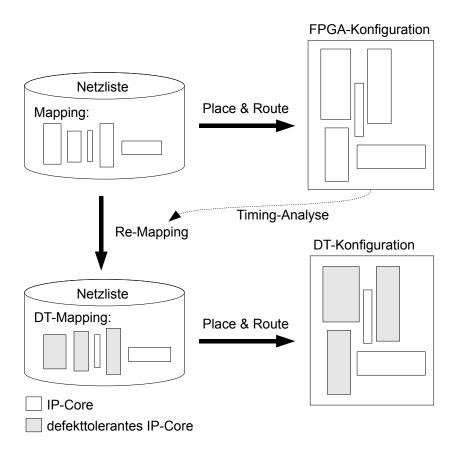

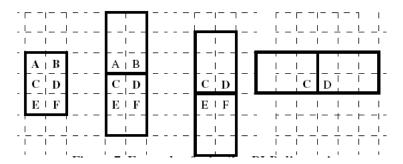

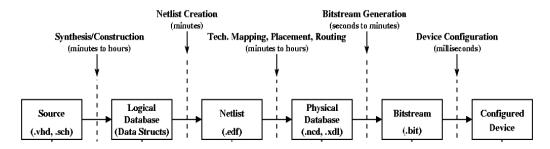

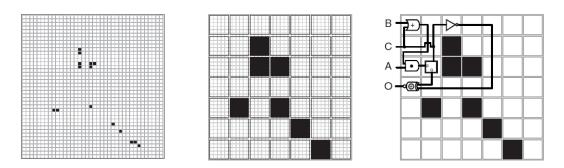

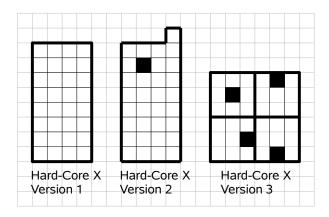

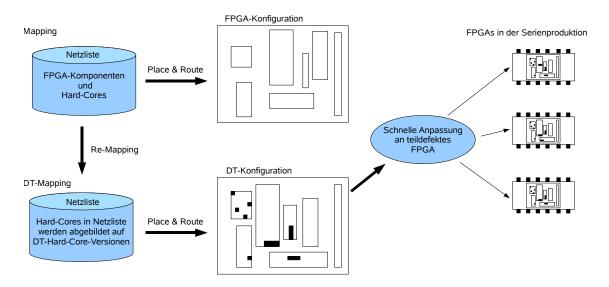

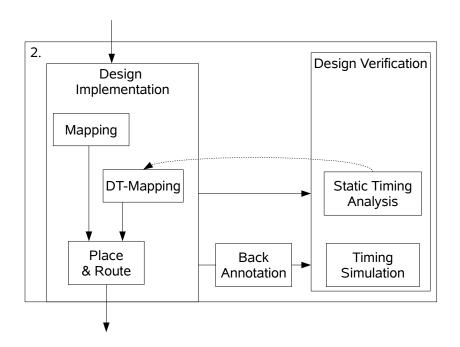

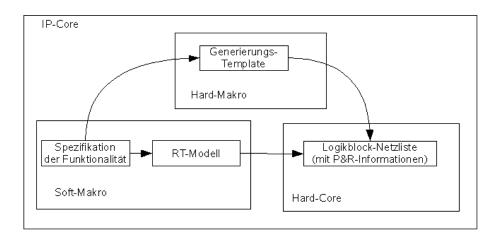

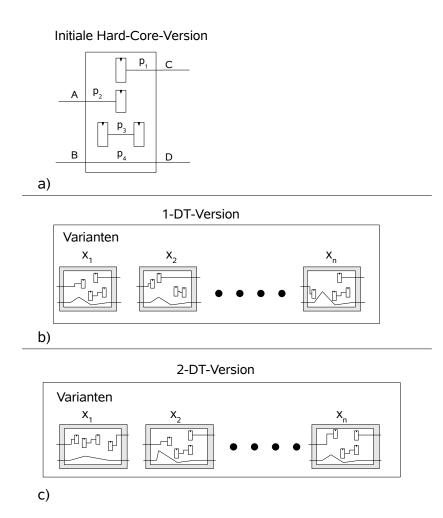

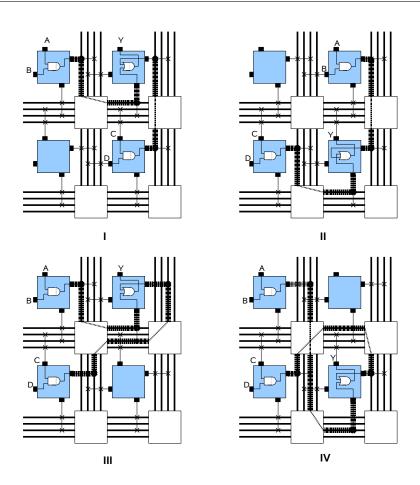

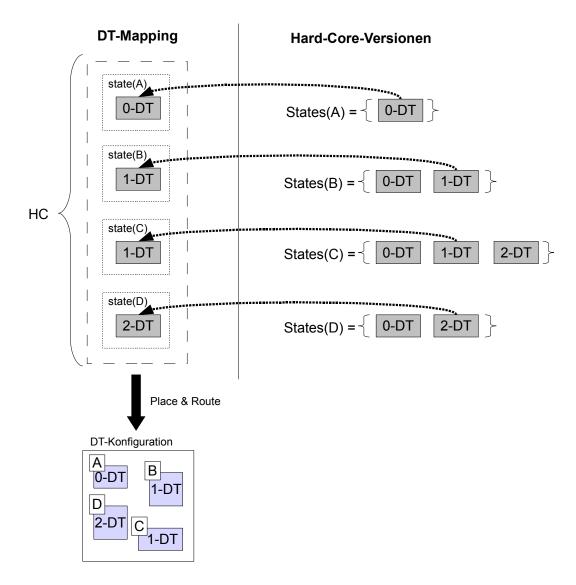

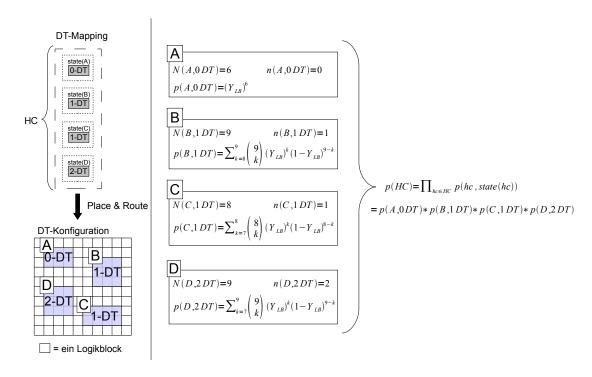

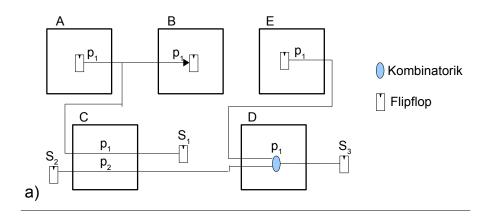

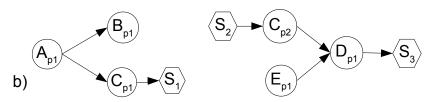

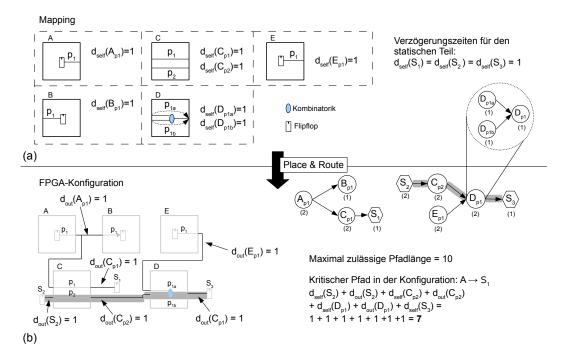

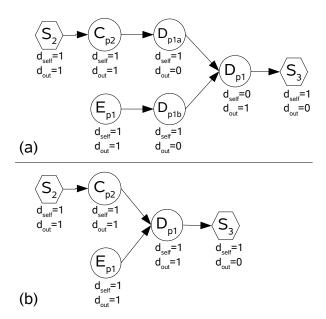

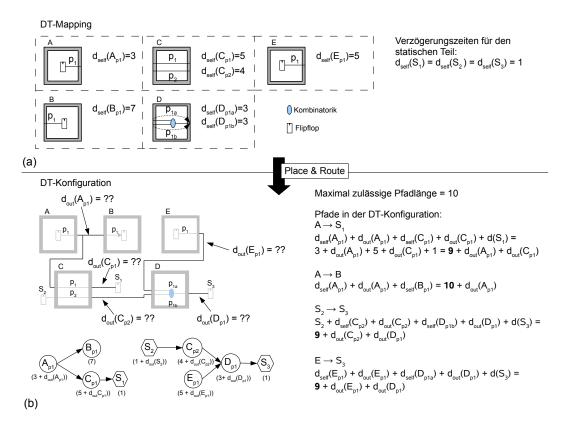

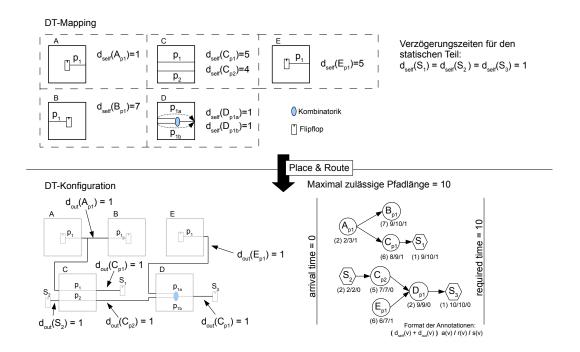

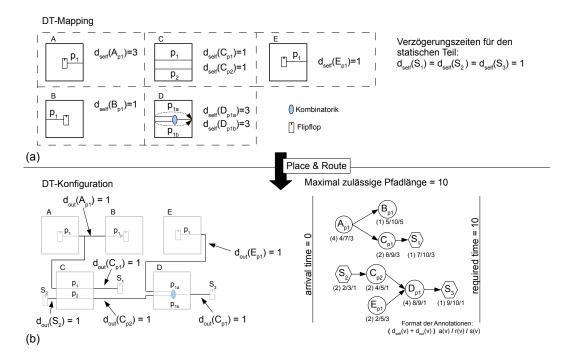

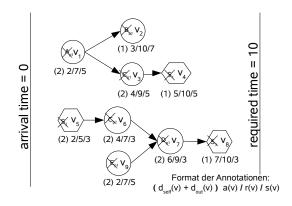

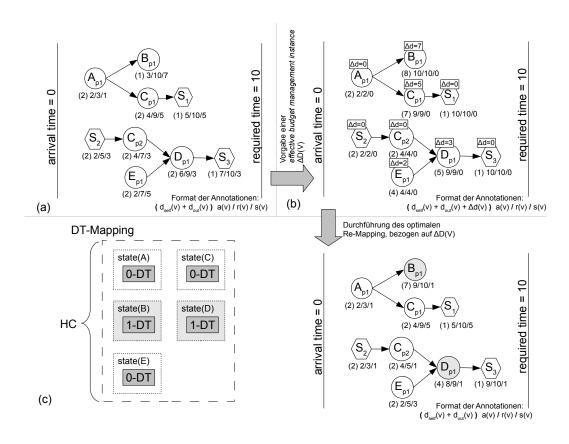

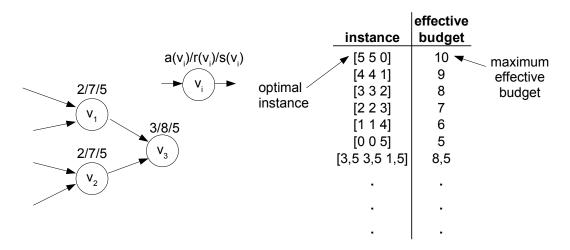

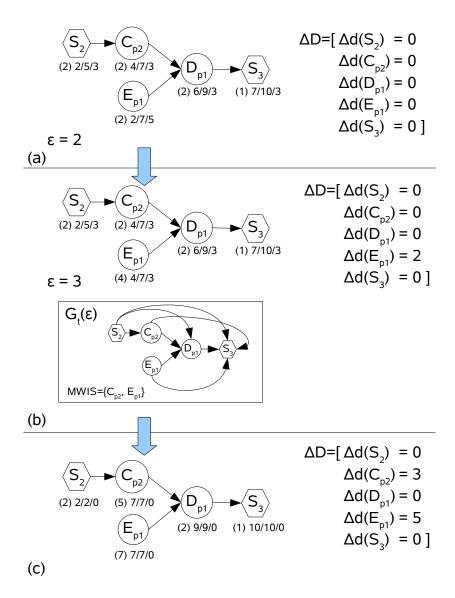

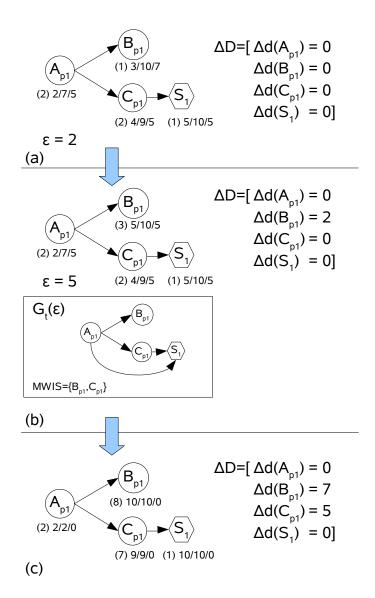

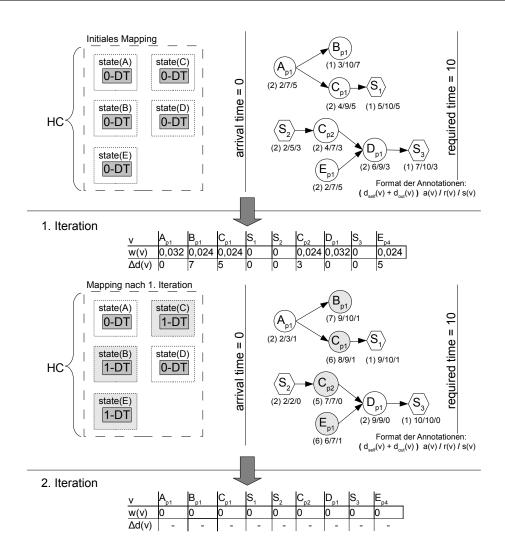

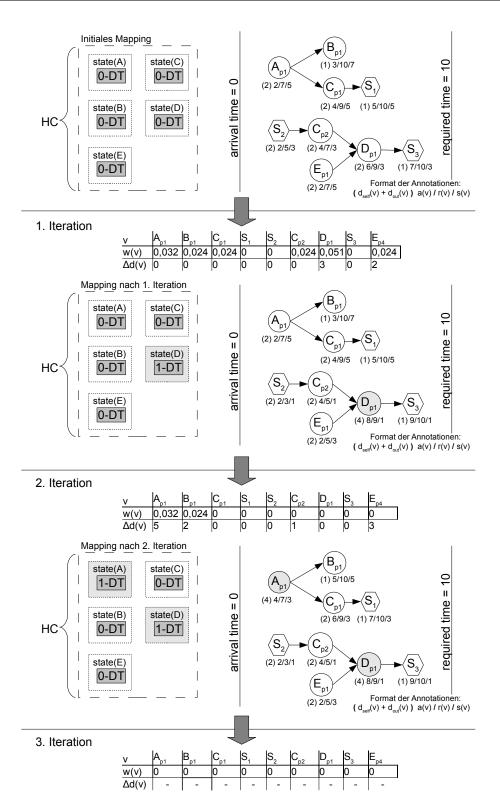

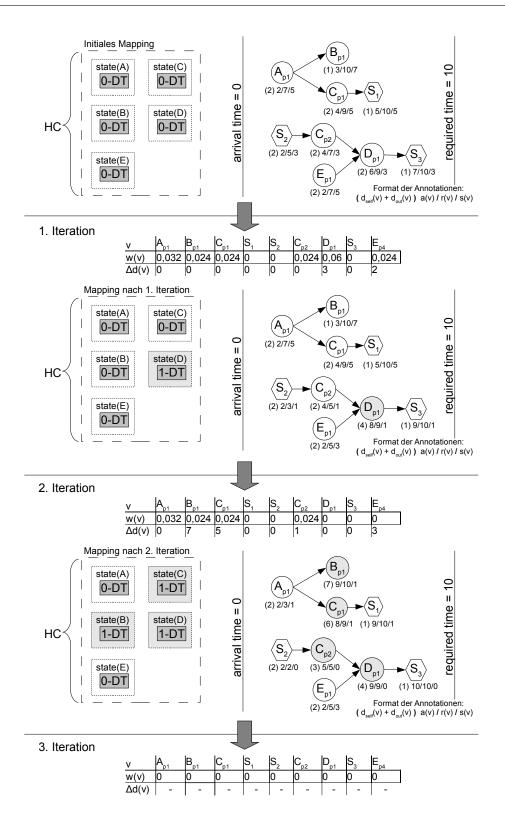

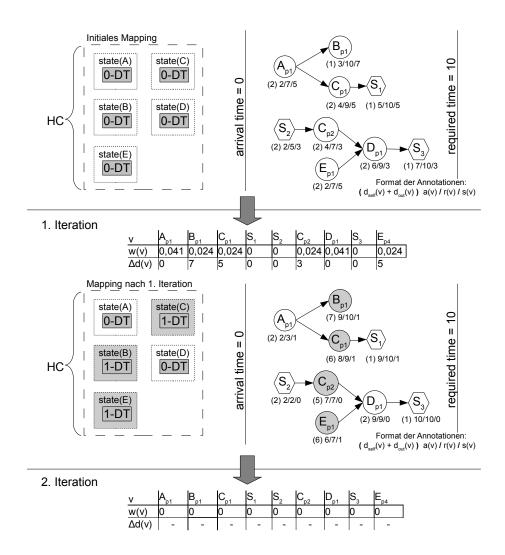

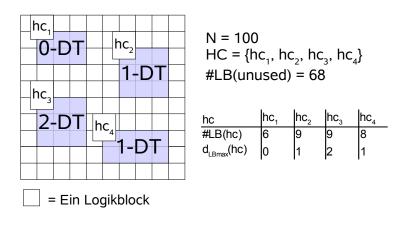

In der vorliegenden Arbeit wurde erstmals ein Verfahren entwickelt, das IP-Cores in einer späten Phase des Design-Flows durch defekttolerante IP-Cores ersetzt. Abbildung 1.1 skizziert diesen Vorgang im Hard-Core basierten Verfahren. Die Schaltungsbeschreibung, die in Form einer Netzliste vorliegt, wird zunächst, wie im ursprünglichen Design vorgesehen, auf eine FPGA-Konfiguration abgebildet. Das über eine statische Timing-Analyse ermittelte Zeitverhalten der Schaltung innerhalb der FPGA-Konfiguration wird als Grundlage für das Re-Mapping der ursprünglichen IP-Cores herangezogen. Ein Re-Mapping, und somit die Einführung von defekttoleranten Schaltungsteilen, findet nur für IP-Cores statt, in denen für das Zeitverhalten dieser Schaltungsteile im ungünstigsten Fall ausreichend Slack vorhanden ist. Durch dieses Vorgehen wird die Timing-Closure<sup>2</sup> für den abschließenden Place&Route-Vorgang, der aus dem DT-Mapping eine DT-Konfiguration erzeugt, erleichtert.

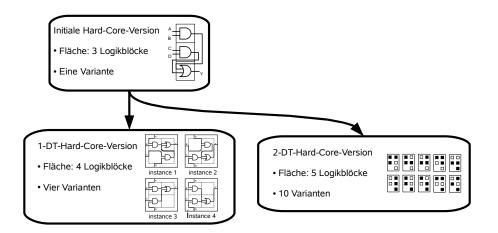

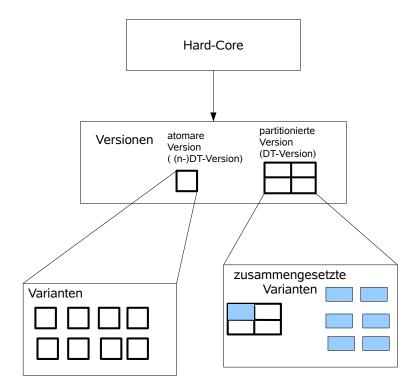

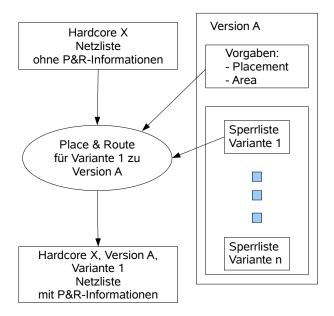

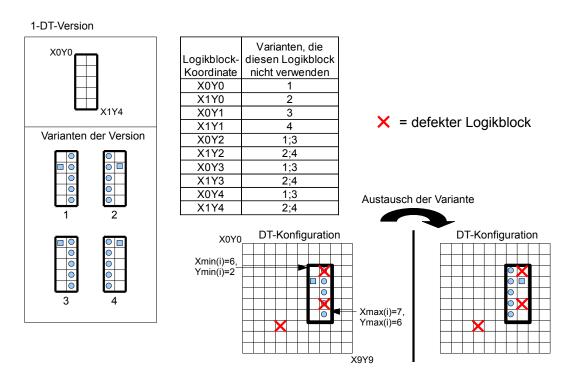

Für die Anpassung der defekttoleranten Schaltungsteile an ein defektes FPGA wurde in der vorliegenden Arbeit ein Verfahren entwickelt, das auf einer Idee basiert, die erstmals von Lach et al. [LMSP98a] vorgestellt wurde. Für jedes IP-Core werden mehrere Ausführungen erstellt, die räumlich unterschiedlich verteilt realisiert sind. Bei einer defekten Teil-Schaltung in einem FPGA wird bei dessen Programmierung wenn möglich eine Ausführung des IP-Cores verwendet, die diese Teil-Schaltung für die korrekte Funktion nicht benötigt.

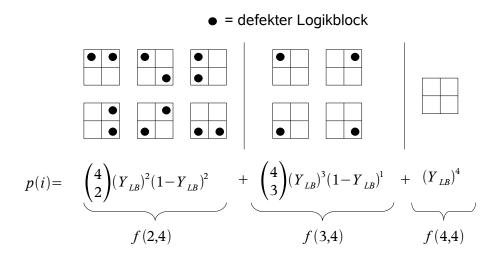

Das Verfahren kann defekte FPGAs nur dann nutzen, wenn die defekten Schaltungsteile sich ausschließlich auf die Logikblöcke dieser FPGAs auswirken. Da von den FPGA-Herstellern keine Informationen herausgegeben werden, aus denen Rückschlüsse auf den bei der Herstellung der FPGAs erzielten Yield möglich sind, konnte im Rahmen dieser Arbeit nur eine grobe Abschätzung der möglichen Steigerung des Yields, die entsteht, wenn FPGAs mit defekten Logikblöcken genutzt werden können, erfolgen. Diese Abschätzung wurde basierend auf einem gängigen Ausbeutemodell vorgenommen und führt zu dem Ergebnis, dass der *random yield* bei einem ursprünglichen Wert von  $Y_{RANDOM} = 0,5$  auf  $Y_{RANDOM} = 0,66$  verbessert wird, wenn 40% der auf dem Chip im Durchschnitt auftretenden Defekte auf einen Logikblock begrenzt sind und FPGAs mit defekten Logikblöcken nicht als Ausschuss, sondern als verwendbare Chips betrachtet werden. Wenn man von  $Y_{RANDOM} = 0,8$  ausgeht, kann unter den gleichen Bedingungen eine Verbesserung auf  $Y_{RANDOM} = 0,875$  erreicht werden. Um einen Anreiz für den Kunden des FPGA-Herstellers zu schaffen, defekte FPGAs in der Serienproduktion

<sup>&</sup>lt;sup>2</sup>, Timing-Closure" beschreibt die Back-End-Aufgabe, die sich damit auseinandersetzt, das vom Front-End-Designer erwartete Zeitverhalten (Timing) zu erreichen bzw. zu implementieren.

Abbildung 1.1: Das Re-Mapping im Hard-Core basierten Verfahren

einzusetzen, müssten defekte FPGAs jedoch günstiger als voll funktionsfähige FPGAs angeboten werden.

### 1.4 Inhaltsübersicht

Der weitere Aufbau der Arbeit gliedert sich wie folgt: **Kapitel 2** stellt einige Grundlagen vor, die für das Verständnis der folgenden Kapitel erforderlich sind. Da der in dieser Arbeit vorgeschlagene Ansatz auf einer vorherigen Diagnose der defekten FPGAs basiert, die mit den zur Zeit in der Herstellung von FPGAs üblichen Testmethoden nicht wirtschaftlich durchgeführt werden kann, stellt **Kapitel 3** Forschungen zu alternativen Diagnose-Verfahren vor, die eine Reduzierung der Kosten für die Diagnose eines FPGAs zum Ziel haben. **Kapitel 4** stellt im Anschluss daran andere Ansätze für die Nutzung von defekten FPGAs vor und vereinfacht durch eine Klassifizierung dieser Ansätze einen späteren Vergleich mit dem in dieser Arbeit entwickelten Verfahren. In **Kapitel 5** werden dann, nach einem ersten groben Überblick, alle Komponenten des in dieser Arbeit vorgeschlagenen Ansatzes ausführlich vorgestellt. In **Kapitel 6** erfolgt schließlich eine ausführliche Bewertung des Ansatzes und ein Vergleich mit den in Kapitel 4 dargestellten, vergleichbaren Arbeiten.

## 2 Grundlagen

Im diesem Kapitel werden Grundlagen dargestellt, die für ein Verständnis dieser Arbeit sinnvoll sind und es wird für die einzelnen Bereiche auf weiterführende Literatur verwiesen.

### 2.1 Aufbau eines FPGAs

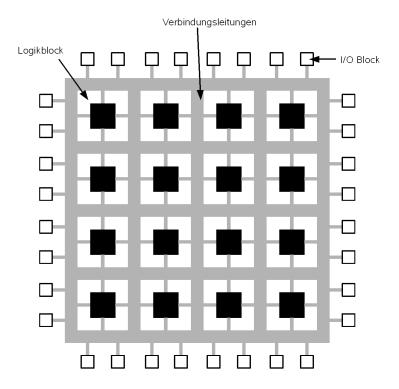

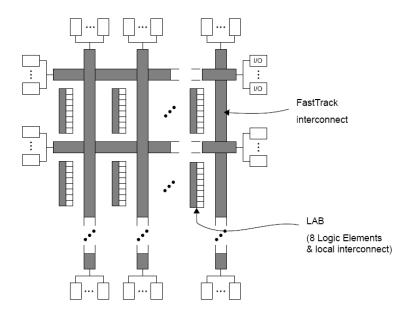

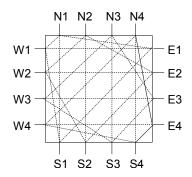

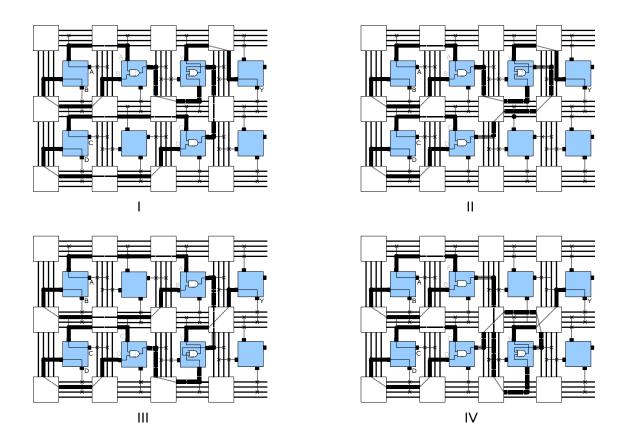

Ein Field Programmable Gate Array (FPGA) ist ein programmierbarer Logikbaustein, der die Realisierung von digitalen logischen Schaltungen ermöglicht. Er besteht aus einer zweidimensionalen programmierbaren Schaltmatrix (engl. *Array*). Abbildung 2.1 zeigt die Hauptbestandteile dieser Matrix.

Die I/O Blöcke können als Eingabe-Block (engl. *Input*) oder Ausgabe-Block (engl. *Output*) konfiguriert werden und sind mit den Pins des FPGA-Bausteins verbunden, um eine Kommunikation mit der Außenwelt zu ermöglichen. Jeder Logikblock wird so konfiguriert, dass er einen Teil der zu realisierenden Schaltung implementiert. Die mit Hilfe der Logikblöcke implementierten Schaltungsteile werden durch ein programmierbares Netzwerk von Verbindungen (engl. *Routing*) untereinander und mit den I/O-Blöcken verbunden. Im Folgenden soll nach einer kurzen Beschreibung des Aufbaus eines Logikblocks auf Besonderheiten in der Anordnung der programmierbaren Verbindungen in unterschiedlichen FPGA-Architekturen eingegangen werden.

## 2.1.1 Aufbau eines Logikblocks

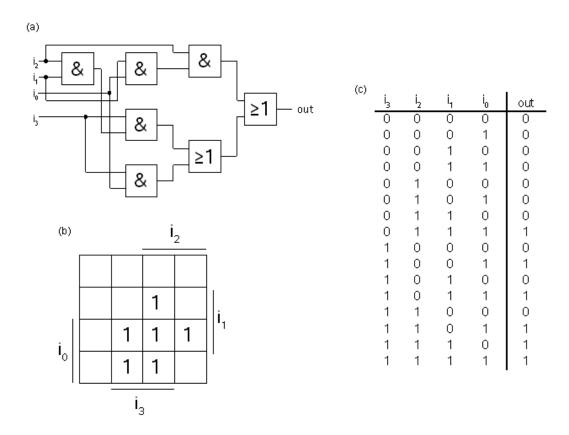

Um ein Schaltnetz in einem FPGA zu implementieren, werden die Schaltfunktionen nicht, wie aus dem VLSI-Entwurf bekannt, durch einzelne Gatter, sondern durch spezielle programmierbare Speicherbausteine, sogenannte *look-up table* (LUT) oder/und Multiplexer realisiert. Abbildung 2.2 zeigt die Schaltfunktion  $out = i_0 i_3 \lor i_1 i_2 i_3 \lor i_0 i_1 i_2$  in verschiedenen Darstellungen.

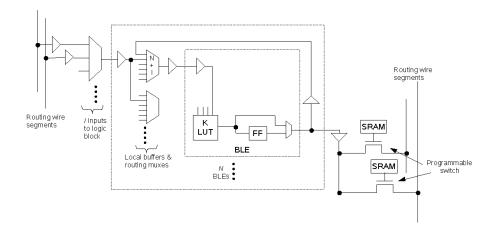

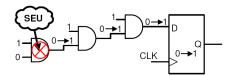

Damit es möglich ist, neben digitalen Schaltnetzen in einem FPGA auch Schaltungen mit Speicherverhalten zu realisieren, enthält ein Logikblock neben den Komponenten für die Realisierung von logischen Schaltfunktionen zusätzlich Flipflops. Abbildung 2.3 skizziert den Aufbau eines Logikblocks.

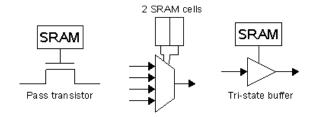

Abbildung 2.1: Hauptbestandteile eines FPGAs [REGSV93]

Der hier abgebildete Logikblock enthält N Logik-Elemente (engl. basic logic elements – BLE), die jeweils ein LUT mit k Eingängen enthalten. Der Ausgang des LUT wird über einen Multiplexer, entweder direkt oder über ein Flipflop, mit dem Ausgang des BLE verbunden. Die I Eingänge und N Ausgänge des Logikblocks sind durch eine Multiplexer-Schaltung an dem Eingang jedes LUT verfügbar. In der Abbildung wird die Programmierung zwischen den Logikblöcken des FPGAs und den Verbindungen zu anderen Logikblöcken (Routing wire segments) über SRAM-Zellen skizziert (Programmable switch). Abbildung 2.4 zeigt drei verschiedene Arten von Schaltern, die in SRAM-FPGAs eingesetzt werden, um diese Verbindungen zu realisieren. Andere Ansätze für die Programmierung der in einem FPGA enthaltenen programmierbaren Schalter, wie z.B. EPROM-Zellen oder Antifuse, werden innerhalb dieser kurzen Einführung in den Aufbau eines FPGAs nicht näher erläutert, da die für die Programmierung benutzte Technologie keine Auswirkungen auf den im Folgenden erläuterten Ansatz hat.

## 2.1.2 Programmierbare Verbindungsleitungen

Im Handel erhältliche FPGAs können bzgl. der Struktur des Verbindungsnetzwerkes zwischen den Logikblöcken und den I/O-Blöcken in drei Gruppen eingeteilt werden [BRM99]: *island-style*, *hierarchical* und *row-based* FPGAs.

Abbildung 2.2: Darstellung einer Schaltfunktion als (a) Gatternetzliste, (b) KV-Diagramm und (c) Inhalt eines LUT

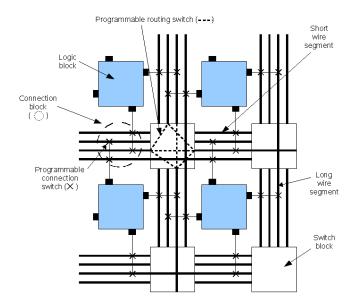

#### Verbindungsstruktur im island-style FPGA

Das zunächst betrachtete *island-style* FPGA-Modell ist in der Forschergemeinde weit verbreitet [CCP06]. Abbildung 2.5 skizziert die Verbindungsstruktur eines *island-style* FPGA. Die Logikblöcke sind jeweils von kurzen Anschlussleitungen umgeben (jeweils vier, in dem hier abgebildeten Modell), die über programmierbare Schalter mit den umliegenden Leitungen verbunden werden können (*programmable connection switch*). Diese Schalter werden zusammengefasst als *connection block* bezeichnet. An den Kreuzungspunkten der horizontal und vertikal angeordneten Verbindungsleitungen sind verschiedene Leitungslängen skizziert: Leitungen, die mehrere Kreuzungspunkte überspannen (*Long wire segment*) und Leitungssegmente, die durch Schalter, die unter der Bezeichnung *switch block* zusammengefasst werden, mit anderen Leitungssegmenten verbunden werden können, um eine längere Leitung zu bilden. Diese Leitungen in verschiedenen Längen sind ein wichtiger Bestandteil eines FPGAs, da jeder Schalter innerhalb einer längeren, d.h. unter Umständen aus mehreren kurzen Leitungssegmenten zusammengesetzten, Verbindung den Widerstand und somit das Delay der Verbindung

Abbildung 2.3: Ein detailliert dargestellter Logikblock [CCP06]

Abbildung 2.4: Verschiedene, in SRAM-FPGAs verwendete Schalter [BRM99]

sowie die insgesamt für das FPGA benötigte Fläche erhöht. Kurze Leitungssegmente sind allerdings von Vorteil, sobald ein Teil eines *long wire segments* nicht benötigt wird. In diesem Fall würde das *long wire segment* die zu treibende Kapazität und damit das Delay der Verbindung, sowie die für die Verbindung auf dem FPGA benötigte Fläche erhöhen [BR99].

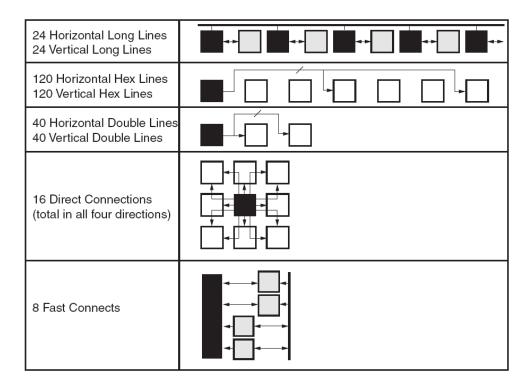

Im Handel erhältliche FPGAs mit einer *island-style-*Architektur stellen daher eine Auswahl von verschiedenen Verbindungslängen mit einer unterschiedlichen Anzahl von Schaltern und Verbindungsmöglichkeiten zur Verfügung. Als Beispiel zeigt Abbildung 2.6 die Verbindungsmöglichkeiten in einem Xilinx Virtex-II FPGA.

Das Delay der Verbindungsleitungen in einem FPGA ist, aufgrund der Auswirkungen von kleinen Änderungen auf die Verzögerungszeiten und somit auf die Performance der durch das FPGA realisierten Schaltung, innerhalb der hier vorliegenden Arbeit besonders zu berücksichtigen:

"Given the large resistances and capacitances involved, it is no surprise that FPGA routing delay is critical. [...] It is not the magnitude of the delay, but the character of the delay that causes routing problems. FPGA delay

Abbildung 2.5: Ein island-style FPGA [BRM99]

comes in large increments, so a small change in path length can make a large difference in delay. [...]" [Tri95]

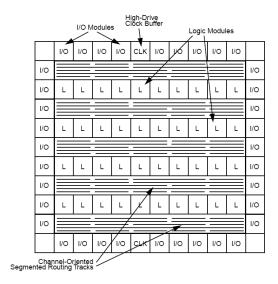

#### Verbindungsstruktur im row-based FPGA

Abbildung 2.7 zeigt die grundlegende Architektur von *row-based* FPGAs, wie sie z.B. von der Firma Actel angeboten werden [Act97]. In dieser Architektur sind die Verbindungsleitungen ausschließlich horizontal angeordnet. Auch in dieser Architektur gibt es Verbindungsleitungen mit unterschiedlichen Längen, die über Schalter miteinander verbunden werden (*Segmented Routing Tracks*). Die Logikmodule (*Logic Modules*) sind einfacher aufgebaut als die bisher betrachteten Logikblöcke, sollen aber im Rahmen dieser Arbeit nicht näher betrachtet werden.

#### Verbindungsstruktur im hierarchical FPGA

Der FPGA-Hersteller Altera bietet FPGAs an, deren Verbindungsstruktur hierarchisch (hierarchical) aufgebaut ist. Abbildung 2.8 (übernommen aus [BR96]) zeigt den Aufbau eines Flex 8000 FPGAs von Altera. Ein Logikblock (logic array block – LAB) besteht in dieser Architektur aus acht Logikelementen und einer lokalen Verbindungsstruktur zwischen diesen Logikelementen. Diese lokale Verbindungsstruktur wird ausschließlich für die Verbindung zwischen den Logikelementen verwendet. Die Zeilen

Abbildung 2.6: Verbindungsmöglichkeiten in einem Xilinx Virtex-II FPGA [Xil07b]

und Spalten des FPGA beinhalten ausschließlich Verbindungsleitungen, die die gesamte Breite, bzw. Höhe des FPGAs abdecken. Die Zeilen des FPGA werden für die Verbindung der LAB untereinander verwendet und die Spalten verbinden die Zeilen untereinander. Durch die Verwendung der Verbindungsleitungen in den Spalten, Zeilen und an den Logikblöcken für jeweils nur eine Aufgabe konnte Altera diese Verbindungen für ihre jeweilige Aufgabe optimieren. Ein weiterer Vorteil dieser hierarchisch aufgebauten Verbindungsarchitektur ist eine genauere Vorhersage der Verbindungszeiten zur Unterstützung des *Place&Route-*Vorgangs, verglichen mit der Vorhersage der Verbindungszeiten in *island-style* FPGA [WL94]. FPGA-Architekturen, auf denen die Verbindungsleitungen die gesamte Breite, bzw. Höhe des FPGAs abdecken, werden auch als Bus-basierte FPGA-Architekturen (*bus based*) bezeichnet.

Abbildung 2.7: Die grundlegende Architektur der FPGAs der Firma Actel

Abbildung 2.8: Die Architektur eines Altera Flex 8000 FPGAs [BR96]

## 2.2 Rechnergestützter Schaltungsentwurf für FPGAs

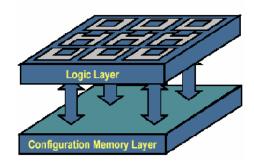

Die Realisierung einer Schaltung auf einem SRAM-FPGA geschieht, wie bereits weiter oben erwähnt, durch die Belegung von Speicherzellen, die dann für eine entsprechende Konfiguration des FPGA sorgen. Im Folgenden wird diese Belegung der Speicherzellen als *FPGA-Konfiguration* bezeichnet. Abbildung 2.9 stellt ein FPGA in zwei Ebe-

nen dar: Die Realisierung der Schaltung erfolgt durch Elemente im *Logic Layer*, die durch die Speicherzellen im *Configuration Memory Layer* konfiguriert werden. Nachdem im nächsten Abschnitt der allgemeine Entwurfsablauf (engl. *design flow*) beschrieben worden ist, dessen Ziel eine FPGA-Konfiguration ist, geht Abschnitt 2.2.2 auf den zunehmend IP-basierten FPGA-Entwurf ein. Eine wichtige Unterstützung für die im Entwurfsablauf genutzten Entwurfswerkzeuge stellt die Timing-Analyse dar. Da die Timing-Analyse im Hard-Core basierten Ansatz von besonderer Bedeutung ist, wird der Ablauf dieser Analyse kurz in Abschnitt 2.2.3 erläutert.

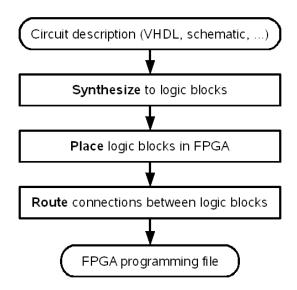

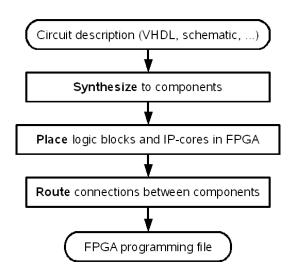

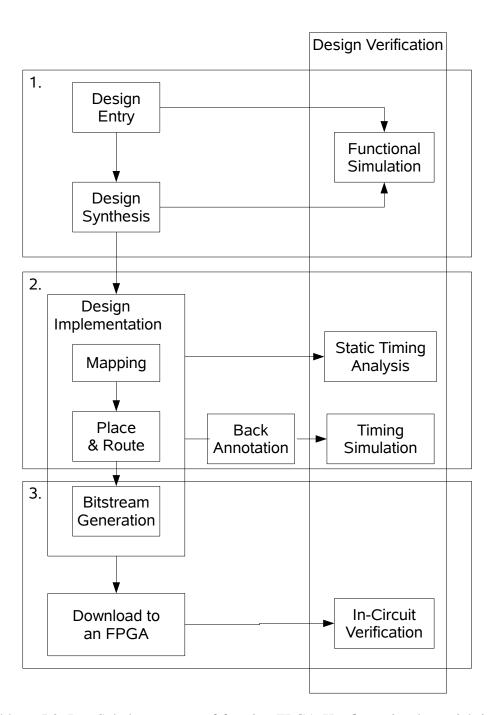

### 2.2.1 Allgemeiner Entwurfsablauf

Um die zu implementierende Schaltung für die Entwurfswerkzeuge verständlich zu beschreiben, nutzen FPGA-Schaltungsdesigner eine graphische Schaltplaneingabe (engl. *schematic entry*) oder eine Hardwarebeschreibungssprache, in der Regel VHDL oder Verilog. Die durch den FPGA-Hersteller bereitgestellten Entwurfswerkzeuge ermöglichen die automatische Generierung einer FPGA-Konfiguration aus dieser Schaltungsbeschreibung. Abbildung 2.10 zeigt den Weg von der Schaltungsbeschreibung zu einer FPGA-Konfiguration.

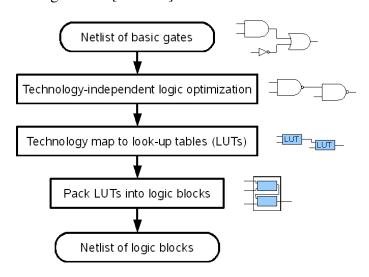

Innerhalb der in der Abbildung beschriebenen Synthese (*Synthesize to logic blocks*) besteht der erste Schritt darin, die Beschreibung der Schaltung in eine Gatternetzliste umzuwandeln. Nach einer technologieunabhängigen Optimierung, wird diese Gatternetzliste in eine Logikblock-Netzliste konvertiert. Ziel dieser in Abbildung 2.11 skizzierten Konvertierung ist die Minimierung der Anzahl der verwendeten Logikblöcke und/oder die Maximierung der Geschwindigkeit der Schaltung.

Bei der anschließenden Platzierung und Verdrahtung der Logikblöcke auf dem FPGA (engl. *Place & Route*, siehe auch Abbildung 2.10) wird jeder Logikblock aus der Netzliste derart auf dem FPGA platziert, dass verbundene Logikblöcke möglichst dicht zusammen liegen (*wire-length-driven placement*) und/oder die Geschwindigkeit der

Abbildung 2.9: Die Konfiguration eines FPGA

Abbildung 2.10: FPGA-Schaltungsdesign: Der automatisierte Weg zur FPGA-Konfiguration [BRM99]

Abbildung 2.11: Details aus der Synthese [BRM99]

Schaltung bzgl. vorgegebener Timing-Constraints optimiert wird (*timing-driven place-ment*). Erst nach dem vollständigen Place & Route kann die Schaltung zeitgenau analysiert und simuliert werden, da die verwendeten Verbindungsleitungen und damit die Verzögerungszeiten (engl. *Delay*) der Verbindungen erst zu diesem Zeitpunkt feststehen. Die Anzahl der auf einem Chip möglichen Transistoren steigt mit jeder Prozessgeneration. Gründe dafür sind verbesserte Auflösungen für die bei der Chip-Herstellung verwendeten Lithografie, aber auch andere Verbesserungen der Produktionsbedingungen, die es erlauben, immer größere Chips zu produzieren. Während in den ersten FPGAs nur

wenige Gatter nachgebildet werden konnten, enthalten die mit den neuesten Prozesstechnologien gefertigten FPGAs zehntausende von Logikblöcken <sup>1</sup> sowie zusätzliche festverdrahtete und in das FPGA eingebettete Komponenten (Multiplizierer / Speicher / Prozessoren). Die ständige Weiterentwicklung der von den Herstellern bereitgestellten Entwurfswerkzeuge unterstützt den Schaltungsdesigner bei der Ausnutzung dieser festverdrahteten eingebetteten Komponenten.

#### 2.2.2 IP-basierter Entwurf

Bereits 1998 wurde durch den damaligen Vizepräsidenten des FPGA-Herstellers Quicklogic, John Birkner, ein Vergleich der damals noch schwach ausgeprägten Wiederverwendung von bereits erstellten Teilschaltungen, bezeichnet als IP-cores, in FPGA-Designs mit der Verwendung von Standard-Logik-Chips in der digitalen Elektronik, die in den 70er Jahren durch das Erscheinen der 74xx-Serie von der Firma Texas Instruments begann, vorgeschlagen:

"Back then, when a design project required an arithmetic logic unit, ALU, the best solution, was an off-the-shelf, standard product, 74181 series TTL device. These were available from a variety of sources in a number of speed and power options. [...] Designers found they could get to market faster with lower cost and higher performance by using standard product 7400-series multiplexors, decoders, registers, counters, adders, ALUs, and register files, compared to proprietary hand crafted functions constructed from gates and flip flops. We didn't call those functions intellectual property or IP cores in those days – we called them standard products." [Bir98]

Seit 1998 hat sich die Anzahl der angebotenen IP-cores als Standard-Komponenten für den Einsatz auf FPGAs deutlich vergrößert. Für die Hersteller bot sich bei dieser Entwicklung die Möglichkeit, durch kostenlos erhältliche IP-cores komplexe Funktionen auf die Architektur ihrer FPGAs zu optimieren und, neben einer Vereinfachung des Designs für den FPGA-Schaltungsdesigner, durch diese optimierten IP-Cores auch den Wechsel eines Kunden auf die FPGAs eines anderen Herstellers zu erschweren. Mit zunehmender Größe der auf dem Markt verfügbaren FPGAs und der zunehmenden Verbreitung von FPGAs, wächst aber auch der Anteil an IP-Cores, für deren Einsatz eine einmalige Lizenzgebühr an den FPGA-Hersteller gezahlt wird. In den letzten Jahren sind zusätzlich Drittanbieter von IP-Core für FPGA hinzugekommen<sup>2</sup>.

<sup>&</sup>lt;sup>1</sup>Der zur Zeit größte verfügbare FPGA der Firma Xilinx, der Virtex-5 XC5VFX200T enthält 30720 sogenannte "slices", die jeweils aus vier BLEs bestehen. Jeweils zwei Slices bilden einen Logikblock [Xil08].

<sup>&</sup>lt;sup>2</sup>Einige dieser Anbieter haben sich der "SignOnce IP License" angeschlossen, die von der Firma Xilinx im September 2001 geschaffen wurde, um die Lizensierung von IP-Cores verschie-

Den oft hohen Kosten für die Entwicklung eines IP-Core für ein ASIC steht eine Lizenzgebühr gegenüber, die von dem Nutzer eines IP-Cores einmalig an den IP-Core Anbieter gezahlt wird. Diese hohen Kosten erschweren den Einsatz von IP-Core für FPGAs, die oft für Produktionen mit einer kleinen oder mittleren Stückzahl eingesetzt werden. Die IP-Core Anbieter für FPGAs sind daher gefordert neue Modelle für die Lizenzierung von IP-Cores zu entwickeln und für deren technische Realisierbarkeit zu sorgen. Denkbar sind z.B. Lizenzgebühren, die von der produzierten Stückzahl des Produktes abhängen [Kea02] oder nach einer festgelegten Zeit erneuert werden müssen [CK06].

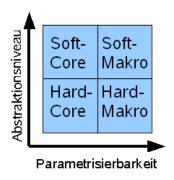

Abbildung 2.12: Soft vs. Hard / Makro vs. Core

Trotz des großen Angebotes von kostenlosen und günstigen IP-Cores für FPGAs durch die FPGA-Hersteller und trotz den in der Praxis oft noch nicht vorhandenen technischen Voraussetzungen für die Nutzung eines angepassten Lizenz-Modells, hat sich der Markt für IP-Cores vor allem durch die Möglichkeit, ganze System on Chip auf einem FPGA zu platzieren, in den letzten Jahren vergrößert. Die steigende Komplexität der FPGA-Designs und die immer wiederkehrende Nutzung von gleichen Standard-Komponenten, wie z.B. Bus-Interfaces oder Signalverarbeitungsblöcken, in einem System on Chip, sorgen dafür, dass der Aufwand für die Erstellung eines neuen FPGA-Designs durch die Verwendung von IP-Cores erheblich verringert werden kann.

Allgemein können die für das Design einer Schaltung auf einem FPGA wiederverwendbaren Schaltungsteile in verschiedenen Formen zur Verfügung gestellt werden. Je nach Form werden sie auch als Hard-Makro, Hard-Core, Soft-Makro und Soft-Core bezeichnet (siehe Abbildung 2.12).

dener Anbieter für die Nutzung in einem Design für Xilinx-FPGAs zu vereinfachen. Unter http://www.xilinx.com/ipcenter/signonce.htm findet man eine Auflistung dieser IP-Core Anbieter.

Die Bezeichnungen "Soft-" und "Hard-" bezeichnen in der Regel den Grad der Abstraktion, in der dieser wiederverwendbare Schaltungsteil angegeben wird. "Soft-" deutet auf eine höhere Abstraktionsebene (z.B. eine Hardwarebeschreibungssprache) hin als "Hard-" (z.B. eine Logikblock-Netzliste). Die Bezeichnungen "-Makro" und "-Core" spielen wie in Abbildung 2.12 angegeben auf die Parametrisierbarkeit des wiederverwendbaren Schaltungsteils an. Oft können noch Parameter verändert werden (z.B. die Bitbreite der Ein- und Ausgänge), bevor aus dem "-Makro", automatisiert durch die Entwurfswerkzeuge, ein "-Core" erstellt wird.

In der vorliegenden Arbeit bezeichnet ein Hard-Core einen wiederverwendbaren Schaltungsteil, der bereits in eine Logikblock-Netzliste synthetisiert wurde. Die Logikblöcke in dieser Netzliste wurden bereits relativ zueinander platziert und untereinander verbunden. Somit kann ein Hard-Core als ein fertiger Teil der Schaltung aufgefasst werden, der auf dem FPGA frei platziert werden kann. Eine Verdrahtung der Logikblöcke untereinander ist nach der Platzierung eines Hard-Cores auf dem FPGA nicht mehr notwendig.

Die hier als Hard-Core bezeichnete Form eines IP-Cores wird in anderen Veröffentlichungen auch als *firm IP* bezeichnet, da der Begriff Hard-Core in vielen Veröffentlichungen bereits für die Bezeichnung der auf modernen FPGA enthaltenen festverdrahteten Komponenten, wie z.B. Multiplizierer, Block-RAM oder Prozessoren verwendet wird. Diese festverdrahteten Komponenten werden in der vorliegenden Arbeit *nicht* als Hard-Core bezeichnet<sup>3</sup>.

Ein Hard-Core kann durch das Entwurfswerkzeug als zusätzliches Element für die Zielmenge der Synthese einer Verhaltensbeschreibung angesehen werden (*inferencing*) oder direkt in der Hardwarebeschreibungssprache als Komponente genutzt werden (*instantiation*). Das Ergebnis der Synthese ist dann eine Netzliste, die aus Logikblöcken, IP-Cores und evtl. festverdrahteten FPGA-Elementen, wie z.B. Multiplizierern oder Block-RAMs besteht. Abbildung 2.13 zeigt die Synthese allgemeiner als in Abbildung 2.10 dargestellt.

## 2.2.3 Timing-Analyse

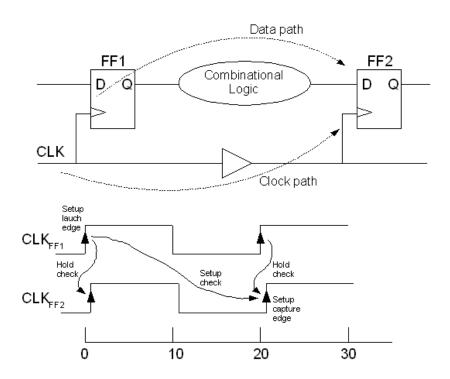

In einer synchronen Schaltung müssen die in einem Flipflop zu speichernden Daten eine bestimmte Zeit vor der das Flipflop steuernden Taktflanke anliegen (Set-Up-Zeit) und nach der Taktflanke noch eine bestimmte Zeit stabil bleiben (Hold-Zeit), um die Übernahme der Daten in das Flipflop zu ermöglichen. Die korrekte Funktion einer FPGA-Konfiguration ist nur dann gewährleistet, wenn diese Zeiten eingehalten werden. Neben

<sup>&</sup>lt;sup>3</sup>Ein Hard-Core kann allerdings auch festverdrahtete Komponenten enthalten. In diesem Fall ist die Platzierbarkeit des Hard-Cores stark eingeschränkt, da von festverdrahteten Komponenten gleicher Art in der Regel nur eine geringe Anzahl auf dem FPGA existiert.

Abbildung 2.13: Eine allgemeinere Darstellung der Erstellung einer FPGA-Konfiguration aus einer Schaltungsbeschreibung

der Länge der Pfade durch ein Schaltnetz ist dabei auch das Verhältnis der Taktflanken zueinander entscheidend.

In Abbildung 2.14 wird für ein einfaches Beispiel mit zwei Flipflops skizziert, welche Zeiträume für eine korrekte Ansteuerung von FF2 berücksichtigt werden müssen.

Eine Verletzung der Set-Up-Zeit ist möglich, wenn die Daten an FF2 nicht rechtzeitig vor der steigenden Flanke an FF2 anliegen. Um dies auszuschließen, muss neben der Set-Up-Zeit des FFs und dem Pfad mit dem längsten Delay auch der kleinstmögliche Taktversatz zwischen den FFs betrachtet werden. Wenn der Taktversatz vernachlässigt wird, kann durch die Ermittlung des Pfades mit dem größten Delay die Taktfrequenz bestimmt werden, mit der die Schaltung maximal betrieben werden kann.

Zu einer Verletzung der Hold-Zeit kann es in der Schaltung kommen, wenn die Daten an FF2 nicht lange genug nach der steigenden Taktflanke anliegen. Für FPGAs werden in der Regel Flipflops eingesetzt, die eine Hold-Zeit von Null haben (zero-hold-time flipflops). Wenn, wie in Abbildung 2.14 verdeutlicht, durch einen Taktversatz (clock skew) das zweite Flipflop später als das erste Flipflop schaltet, kann es allerdings dazu kommen, dass die Daten an dem Flipflop anliegen, bevor die vorherigen Daten übernommen worden sind, so dass auch hier die Hold-Zeit verletzt wurde. Neben dem Pfad mit dem kürzesten Delay, muss also auch der größtmögliche Taktversatz in Betracht gezogen werden, um eine Verletzung der Hold-Zeit an FF2 auszuschließen. Um den Taktversatz möglichst gering zu halten, werden spezielle Verteilungen des Taktsignals (Clock Trees) verwendet. Wenn der maximale Taktversatz kleiner ist als die Summe der Verzögerung des Signals durch ein Flipflop und durch eine zeitlich minimale Verbindung, dann kann innerhalb des FPGAs die Hold-Zeit nicht verletzt werden.

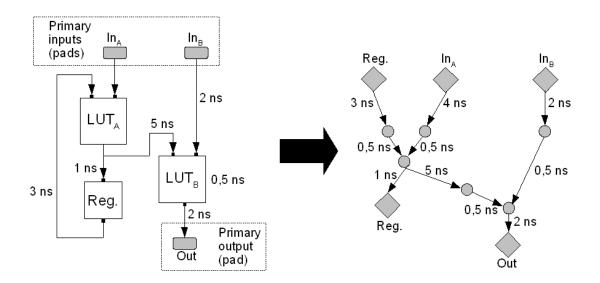

Abbildung 2.14: Die Überprüfung der Setup- (Setup check) und der Hold-Zeit an einem Beispiel mit zwei Flipflops [Syn04]

Die Timing-Analyse [RBHSC82] wird von Entwurfswerkzeugen unter anderem verwendet, um die Taktfrequenz zu ermitteln, mit der eine FPGA-Konfiguration maximal betrieben werden kann. Für diese Analyse wird jedes der in der FPGA-Konfiguration enthaltenen Schaltnetze als gerichteter Graph dargestellt. Eine mögliche Darstellung zeigt Abbildung 2.15. Die Knoten repräsentieren die Ein-und Ausgangs-Pins der in der Schaltung verwendeten Elemente, wie z.B. LUTs und Register. Die Kanten werden zwischen den Eingängen der kombinatorischen Elemente, in einem FPGA also vor allem LUTs, und deren Ausgängen eingezeichnet. Für alle Verbindungen der Elemente der Schaltung untereinander werden ebenfalls Kanten eingezeichnet. An jeder Kante wird nun ein Delay annotiert, das dem Delay für den maximalen Pfad innerhalb eines kombinatorischen Elements bzw. dem Delay für die Verbindung zwischen den Elementen entspricht. Alle Eingänge eines Schaltnetzes, d.h. externe Eingänge, wie in Abbildung  $2.15 \ In_A$  und  $In_B$ , oder die Ausgänge der Register haben keine eingehenden Kanten im Graphen. Alle Ausgänge haben keine ausgehenden Kanten.

Wenn die Anfangsknoten des Graphen mit der Ankunftszeit annotiert werden, lässt sich die minimal für den korrekten Betrieb der Schaltung benötigte Länge einer Taktperiode rekursiv ermitteln mit

$$T_{arrival}(i) = max_{\forall j \in fanin(i)} \{ T_{arrival}(j) + delay(j, i) \} ,$$

Abbildung 2.15: Eine einfache Schaltung als gerichteter Graph dargestellt [BRM99]

wobei i und j Knoten sind, delay(i, j) der Delay-Wert der Kante zwischen den Knoten i und j ist und fanin(i) die Menge aller Vorgängerknoten des Knoten i bezeichnet. Wenn für alle Knoten  $T_{arrival}$  berechnet wurde, definiert der Knoten mit dem größten Wert für  $T_{arrival}$  die minimale Taktperiode für die Schaltung. In dem Beispiel in Abbildung 2.15 ist die minimale Länge der Taktperiode durch den Knoten Out auf 12 ns festgelegt.

Neben der Ermittlung der maximalen Taktfrequenz erlaubt die Timing-Analyse [RBHSC82] die Beurteilung von vorliegenden Timing-Problemen. Wenn eine vorgegebene maximale Taktfrequenz und somit in jedem kombinatorischen Schaltnetz innerhalb einer Schaltung eine maximale Verzögerungszeit eingehalten werden soll, kann für jeden Knoten die Zeit  $T_{required}$  berechnet werden, zu der die Daten an diesem Knoten benötigt werden, damit das Schaltnetz insgesamt die gewünschte maximale Verzögerungszeit einhält. Bezogen auf das oben angegebene Beispiel soll jetzt an den beiden Ausgängen des abgebildeten Schaltnetzes (Reg. und Out) die Ankunftszeit 12 ns annotiert werden. Diese Annotierung beschreibt die Zeit , zu der die Ankunft der Daten erforderlich ist, um die ermittelte maximale Verzögerungszeit einzuhalten. Die erforderliche Ankunftszeit für die restlichen Knoten kann dann wiederum rekursiv berechnet werden mit

$$T_{required(i)} = min_{\forall j \in fanout(i)} \{ T_{required}(j) - delay(i, j) \}$$

.

Eine Metrik dafür, wie wichtig jede der in dem Graphen betrachteten Verbindungen in Bezug auf die Einhaltung der maximalen Verzögerungszeit des Schaltnetzes ist, bietet der Slack, der in dem hier skizzierten Beispiel als

$$slack(i, j) = T_{required}(j) - T_{arrival}(i) - delay(i, j)$$

angegeben werden kann.

**Definition 2.1.** Der Slack ist der Umfang des Delays, das an einem Element, oder der Verbindung zwischen zwei Elementen, zusätzlich genutzt werden kann, ohne dass die maximale Verzögerungszeit des Schaltnetzes erhöht wird<sup>4</sup>. Für alle Elemente und Verbindungen, die auf dem kritischen Pfad liegen, ist der Slack null.

In Abbildung 2.15 führt der kritische Pfad von dem Eingang  $In_A$  zu dem Ausgang Out. Für die Verbindung zwischen  $In_B$  und  $LUT_B$  ist in diesem Beispiel ein Slack von 7,5 ns vorhanden. Diese Verbindung könnte also beispielsweise über eine langsamere Verbindungsleitung laufen, ohne die maximale Verzögerungszeit des Schaltnetzes zu erhöhen. Ein negativer Slack hingegen würde eine Verletzung der maximalen Verzögerungszeit für das Schaltnetz bedeuten. Wenn eine Schaltung nicht mit der gewünschten Verzögerungszeit realisiert werden kann, gibt ein negativer Slack dem Schaltungsdesigner Hinweise darauf, an welchen Stellen Verbindungsleitungen verkürzt bzw. Elemente mit einer geringeren Verzögerungszeit eingesetzt oder andere Maßnahmen zur Senkung der Verzögerungszeit ergriffen werden müssen.

Wenn innerhalb einer Schaltung positiver Slack an allen Pfaden vorhanden ist, die über ein Element dieser Schaltung verlaufen, kann dieses Element aufgrund dieses zusätzlichen Slacks in ein funktional gleiches Element ausgetauscht werden, das z.B. weniger Fläche verbraucht und/oder eine geringere Verlustleistung zur Folge hat. Das *gate sizing*-Problem besteht darin, eine Menge von Gattern in einer Schaltung zu finden, deren Fläche und Verlustleistung durch die Verwendung von kleineren Zellen aus der für den Entwurf einer integrierten Schaltung verwendeten Zellenbibliothek reduziert werden kann, ohne eine vorgegebene maximale Verzögerungszeit zu verletzen [GLPS97]. Auch eine Veränderung der Treshold-Spannung zur Reduzierung der Verlustleistung an diesen Gattern, bzw. eine Kombination aus beiden Techniken [Sri03] wurde als Möglichkeit für die Ausnutzung des Slacks in einer Schaltung erforscht.

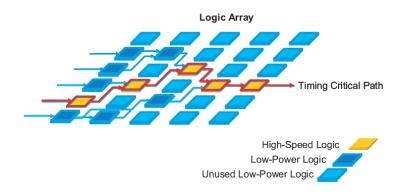

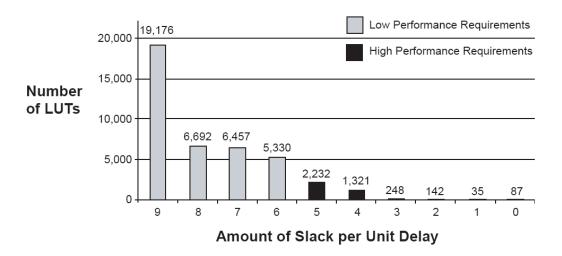

Auch bei einem FPGA kann die Veränderung der Threshold-Spannung an Logikblöcken, an denen Slack vorhanden ist, für eine Reduzierung der Verlustleistung eingesetzt werden. Die Stratix III FPGAs der Firma Altera sind in Bereiche eingeteilt, die mit zwei verschiedenen Threshold-Spannungen betrieben werden können [Alt07]. Abbildung 2.16 skizziert die Verwendung dieser Bereiche. Die "Low-Power"-Logik verursacht weniger Verlustleistung als die "High Speed"-Logik, führt dafür aber zu einem erhöhten Delay des Bereiches. Wieviele und welche der Bereiche als "Low-Power"-Logik betrieben werden können, hängt von dem Slack auf den nicht-kritischen Pfaden und der Aufteilung der Logik auf die Bereiche ab. Die in Abbildung 2.17 gezeigte für diesen Ansatz günstige - Slack-Verteilung ist, nach Angabe der Firma Altera, eine typische Verteilung des Slacks in einem FPGA-Design [Alt07].

<sup>&</sup>lt;sup>4</sup>Dies gilt nur, wenn das Delay der anderen Elemente und Verbindungen konstant bleibt.

Abbildung 2.16: Stratix III Programmable Power Technology [Alt07]

In dem in der vorliegenden Arbeit vorgestellten Ansatz wird der an dem Hard-Core vorhandene Slack ausgenutzt, um die Defekttoleranz innerhalb der Hard-Core und dadurch auch die Defekttoleranz der gesamten Schaltung zu erhöhen.

Abbildung 2.17: Ein Slack-Histogramm, das nach Angabe der Firma Altera eine typische Slack-Verteilung in einem FPGA-Design darstellt, und die Einteilung der LAB nach dem benötigten Delay [Alt07]

## 2.3 Die Ausbeute bei der Herstellung von FPGAs

Die Herstellung eines FPGAs erfolgt als integrierte Schaltung (IC). Auf einer dünnen Scheibe aus Halbleitersubstrat, dem sogenannten Wafer, werden jeweils mehrere ICs gleichzeitig hergestellt. Unter Reinstraum-Bedingungen wird der Wafer im Rahmen dieses Herstellungsprozesses unter Sauerstoffzufuhr erwärmt, wodurch sich eine Siliziumoxidschicht bildet. Im Anschluss daran wird der Wafer mit Photolack beschichtet und über eine Maske belichtet. Durch das Belichten ist der Photolack an einigen Stellen nicht mehr resistent und kann leicht entfernt werden. Die Stellen des Siliziumoxides, die nicht mehr durch Fotolack geschützt sind, können nun weggeätzt werden. Anschließend wird auch der restliche Fotolack entfernt. Die nicht mehr durch Siliziumoxid geschützten Stellen können jetzt in einem Diffusionsofen oder durch Ionenbeschuss dotiert werden. Der beschriebene Ablauf wiederholt sich bei der IC Herstellung mehrfach. Durch voneinander isolierte Metallisierungsschichten und Kontaktierungen durch die Schichten hindurch (Vias) werden anschließend die gewünschten Verbindungen hergestellt. Nachdem der Wafer, unter Aussparung der für die Kommunikation mit der Außenwelt vorgesehenen Stellen, mit einer isolierenden Schicht überzogen worden ist, werden die einzelnen ICs getestet. Jeder Chip, der diesen Test nicht besteht, wird markiert. Alle nicht markierten ICs werden anschließend in ein Gehäuse montiert und nach weiteren Tests für den Verkauf freigegeben.

Im Herstellungsprozess treten Fehler auf, die teilweise zu nicht verwendbaren ICs führen. Diese Fehler können in drei Kategorien eingeteilt werden [FP92]:

**Gross defects** Dieser Bezeichnung werden Fehler zugeordnet, die durch mechanische Beschädigungen des Wafers, z.B. Kratzer oder großflächig nicht vollständig abgetragenes Material, entstehen. Ein *gross defect* betrifft in der Regel einen großen Bereich des Wafers und führt dadurch oft zu einem Verlust in der Ausbeute an funktionierenden ICs.

Parametric defects Alle Fehler, die zu einer Veränderung der elektrischen Parameter führen, werden als *parametric defects* bezeichnet. Ein Beispiel für einen *parametric defect* ist eine ungleichmäßige Verteilung der Dotiersubstanz, die einen unterschiedlichen Widerstand der MOS-Transistoren verursachen kann. *Parametric defects* wirken sich auf die Performance und die Verlässlichkeit der ICs aus und können in extremen Fällen auch zu einem Verlust in der Ausbeute führen.

**Random defects** Alle Fehler, die nicht unter die bisher aufgeführten Kategorien fallen, werden als *random defects* bezeichnet. *Random defects* entstehen oft durch Partikel, die während der Produktion auf dem Wafer liegen und können sich in Form von fehlendem oder zusätzlichem leitenden Material auf den IC auswirken.

Da *gross defects* bei der Herstellung in der Regel auf ein Minimum reduziert werden können und *parametric defects* sich vor allem auf die Verlässlichkeit der ICs und nicht auf die Ausbeute auswirken, werden im Folgenden ausschließlich *random defects* betrachtet. Die Anzahl der auf dem Wafer auftretenden *random defects* kann mit Hilfe der Wahrscheinlichkeitsrechnung vorhergesagt werden.

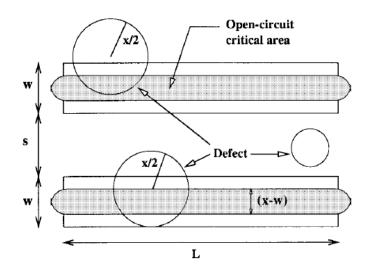

Random defects können in verschiedene Typen unterteilt werden. Fehlendes leitendes Material auf dem Wafer kann eine Leitungsunterbrechung auf dem Chip hervorrufen, zusätzliches leitendes Material einen Kurzschluss. Ob ein random defect tatsächlich zu einer defekten Schaltung führt, hängt also von dem Ort, an dem der Fehler auftritt, der Größe des Fehlers und dem Fehlertyp ab. Durch die idealisierte Annahme eines kreisrunden Fehlers, kann aufgrund des Layouts eines vorliegenden ICs für jede Fehlergröße und jeden Fehlertyp die kritische Fläche  $A_i^{(c)}(x)$  für einen Fehler vom Typ i mit dem Durchmesser x berechnet werden. Nur wenn der Mittelpunkt des betrachteten Fehlers innerhalb dieser kritischen Fläche liegt, führt der Fehler zu einer fehlerhaften Schaltung, und nur dann wird er in der hier vorliegenden Arbeit als ein Defekt bezeichnet<sup>5</sup>. Abbildung 2.18 skizziert die kritische Fläche, für einen Fehler, durch den Material mit dem Durchmesser x auf dem Chip fehlt [KK98]. Nur der untere der drei abgebildeten Fehler führt zu einer offenen Verbindung, also einem Defekt (open circuit fault).

Die Auftrittswahrscheinlichkeit eines Defektes mit einem Durchmesser *x* kann durch die folgende Wahrscheinlichkeitsdichtefunktion angegeben werden [KK07]:

<sup>&</sup>lt;sup>5</sup>In der Ermittlung des Yields wird in den meisten Veröffentlichungen zwischen "defect" und "fault" unterschieden. Ein im Herstellungsprozess entstandener Fehler wird als "defect" bezeichnet. Wenn dieser Fehler zu einer fehlerhaften Schaltung auf dem Chip führt, wird er zu einem "fault". Erst ein "fault" entspricht somit in der hier vorliegenden Arbeit einem Defekt.

Abbildung 2.18: Die kritische Fläche für einen Fehler mit dem Durchmesser x, wenn das Resultat dieses Fehlers fehlendes leitendes Material auf dem Chip ist

$$f_d(x) = \begin{cases} kx^{-p} & wenn \ x_0 \le x \\ 0 & sonst \end{cases}$$

wobei  $k = \frac{(p-1)x_0^{p-1}x_M^{p-1}}{x_M^{p-1}-x_0^{p-1}}$  eine normalisierende Konstante,  $x_0$  die Grenze für die bei der Lithographie verwendeten Auflösung und  $x_M$  der maximale Durchmesser eines Defektes ist. Der Parameter p kann empirisch ermittelt werden und liegt typischerweise zwischen 2 und 3,5 [KK07].

Die Wahrscheinlichkeit  $\Theta_i(x)$ , dass ein Fehler vom Typ i mit dem Durchmesser x einen Defekt verursacht, kann bei Annahme einer Gleichverteilung der Fehler über die Fläche durch

$$\Theta_i(x) = \frac{A_i^{(c)}(x)}{A_{chip}} \tag{2.1}$$

beschrieben werden, wobei  $A_{chip}$  die Gesamtfläche des ICs bezeichnet.

Die durchschnittliche Wahrscheinlichkeit für die Verursachung eines Defektes durch einen Fehler vom Typ i kann dann als ein durch  $f_d(x)$  gewichteter Mittelwert über alle auftretenden Fehlergrößen angegeben werden [KK07]:

$$\Theta_i = \int_{x_0}^{x_M} \Theta_i(x) f_d(x) dx \tag{2.2}$$

Wenn die durchschnittliche Anzahl der Fehler  $d_i$  für jeden Fehler-Typ i pro Flächeneinheit bekannt ist, kann jetzt die durchschnittliche Anzahl von Defekten auf dem Chip, im Folgenden bezeichnet mit  $\lambda$ , errechnet werden:

$$\lambda = \sum_{i} \Theta_{i} A_{chip} d_{i} \tag{2.3}$$

Die Wahrscheinlichkeit, dass *k* Defekte auf dem Chip vorhanden sind, kann bei einer Einteilung der Chipfläche in statistisch voneinander unabhängigen Flächen gleicher Größe durch die Binomial-verteilung angegeben werden. Mit der diskreten Zufallsvariablen

X="Anzahl der Fehler auf dem IC"

und der durchschnittlichen Anzahl von Defekten auf dem IC, also dem Erwartungswert von X

$$E(X) = \lambda$$

gilt dann für n statisch voneinander unabhängige Flächen für die Wahrscheinlichkeit von k Defekten auf dem IC:

$$P(X=k) = \binom{n}{k} \left(\frac{\lambda}{n}\right)^k \left(1 - \frac{\lambda}{n}\right)^{n-k} \tag{2.4}$$

Wenn wir für Formel (2.4)  $n \to \infty$  annehmen, kann die Binomialverteilung durch eine Poisson-Verteilung ersetzt werden:

$$\lim_{n\to\infty} P(X=k) = \lim_{n\to\infty} \binom{n}{k} \left(\frac{\lambda}{n}\right)^k \left(1 - \frac{\lambda}{n}\right)^{n-k} = \frac{e^{-\lambda}\lambda^k}{k!}$$

(2.5)

Für die Wahrscheinlichkeit für einen Chip ohne random defects (k = 0) ergibt sich aus Formel (2.5) dann:

$$Y_{RANDOM} = P(X=0) = e^{-\lambda}$$

(2.6)

Die Wahrscheinlichkeit dafür, dass kein Defekt auf dem FPGA auftritt, entspricht dem Verhältnis von funktionsfähigen FPGAs zu gefertigten FPGAs und wird allgemein als Ausbeute (engl. *chip yield*)  $Y_{chip}$  bezeichnet. Wenn mit  $Y_{GLOBAL}$  die Wahrscheinlichkeit bezeichnet wird, dass kein *gross defect* oder *parametric defect* auf dem FPGA auftritt, gilt

$$Y_{chip} = Y_{RANDOM} * Y_{GLOBAL} = \frac{funktionsfähige FPGAs}{gefertigte FPGAs}$$

(2.7)

Der Hard-Core basierte Ansatz verbessert die Ausbeute durch eine Steigerung der Wahrscheinlichkeit, dass auch ein FPGA mit defekten Logikblöcken genutzt und somit als "funktionsfähiges FPGA" eingestuft werden kann.

# 3 Test und Diagnose von FPGAs

Die Ermittlung von Defekten ist unbedingt erforderlich, um die Qualität der ausgelieferten FPGAs zu gewährleisten. Eine Diagnose, d.h. die Lokalisierung des Defektes, ist jedoch nur notwendig, wenn der Defekt aktiv umgangen werden soll. Wenn die defekten FPGAs nach der Herstellung weggeworfen werden, ist eine Lokalisierung des Defektes sinnlos, es sei denn, diese Lokalisierung findet aus statistischen Gründen statt. In [Mey03] wird die Unterscheidung zwischen Test und Diagnose einer Schaltung wie folgt beschrieben:

"Da der Test Teil der Produktion ist und auf jede produzierte Schaltung angewendet werden muss, sind die Anforderungen an einen optimalen Test, die maximal mögliche Fehlerabdeckung bei minimaler Testdauer und minimaler Größe des Testwertsatzes zu erreichen. Die aus dem Test erhaltenen Informationen können lediglich zur Bestimmung der korrekten Funktion der Schaltung dienen. Die zwangsläufig erwünschte hohe Fehlerabdeckung jedes einzelnen Testmusters geht damit zu Lasten der Aussagekraft, welcher der modellierten Fehler bei einer fehlerhaften Testantwort in der Schaltung vorliegt. Die Diagnose soll, im Unterschied zum Test, die Bestimmung des Fehlerortes innerhalb der Schaltung mit dem Ziel ermöglichen, den dem Fehler zugrunde liegenden Defekt aufzuspüren. Die Anforderungen an die zu verwendenden Testmuster sind - im Gegensatz zum Test - eine möglichst eindeutige Zuordnung zwischen einem modellierten Fehler und einem Testmuster, um für ein ausfallendes Testmuster über eine möglichst geringe Anzahl an von ihm abgedeckten Fehlern die Zahl der in Frage kommenden Fehlerorte gering zu halten. Durch die Verwendung mehrerer Testmuster, die eine unterschiedliche Kombination an Fehlern abdecken, kann die Menge der möglicherweise in der Schaltung vorliegenden Fehler über eine Schnittmengenbestimmung der von den ausfallenden Vektoren detektierbaren Fehler verringert werden."

Wegen der kostspieligen Testzeit wird ein Test bei heutigen Verfahren sofort abgebrochen, wenn ein Fehler detektiert wurde. Die so eingesparte Testzeit ist signifikant, da sehr viele Defekte bereits mit den ersten der angelegten Testmuster detektiert werden können. Eine Diagnose, durch die zusätzliche Kosten für defekte FPGAs entstehen, wird daher generell als nicht wirtschaftlich durchführbar angesehen [Tri08].

Für den in dieser Arbeit vorgestellten Hard-Core basierten Ansatz ist eine Lokalisierung der defekten Logikblöcke, also eine Diagnose der defekt produzierten FPGAs, eine unabdingbare Voraussetzung. Da defekte Logikblöcke umgangen werden, müssen sie zuvor durch eine Diagnose des FPGAs identifiziert werden. Forschungen zu alternativen Diagnose-Verfahren zielen darauf ab, die Kosten für eine Diagnose des FPGAs zu reduzieren. Aufgrund der technologischen Entwicklung wird allgemein vermutet, dass zukünftige FPGA-Generationen deutlich mehr Defekte enthalten, als die zur Zeit produzierten FPGAs. Sinkende Kosten auf der Seite der Diagnose-Verfahren und steigende Kosten aufgrund einer sinkenden Ausbeute an FPGAs könnten so in Zukunft zu wirtschaftlich einsetzbaren Diagnose-Verfahren führen.

Im Gegensatz zu Testverfahren, die mit extern angelegten Testmustern arbeiten, wurden auch Verfahren vorgeschlagen, die auf einem Built-In-Self-Test (BIST) basieren [SMSP98, ASE04, VDS04, SD06]. Diese Ansätze programmieren in der Regel die auf dem FPGA bereits vorhandenen Strukturen für die Durchführung des Tests, d.h. es werden Schaltungsteile des FPGAs für den Test programmiert, die im Anschluss an die Durchführung des BIST wie gewohnt für den laufenden Betrieb verwendet werden können. Es sind somit keine Schaltungen erforderlich, die nur für den Test in das FPGA integriert und nach dem Test nicht mehr verwendet werden. Durch einen BIST können Kosten eingespart werden, die bei einem externen Test für die oft sehr teuren Geräte (meist zusammengefasst unter der Bezeichnung ATE – Automatic Test Equipment) anfallen. Bei einem BIST reduziert sich der Aufwand für das ATE auf die Bereitstellung der FPGA-Konfigurationen, die für die BIST-Logik verwendet werden, die Einleitung der Test-Prozedur und das Auslesen der Test-Resultate und der Diagnose-Daten aus dem FPGA.

Nachdem im nächsten Abschnitt auf die für die Diagnose von defekten FPGAs in akademischen Ansätzen verwendeten Fehlermodelle eingegangen worden ist, erläutert Abschnitt (3.2) zwei grundlegende Verfahren für einen FPGA-BIST, die von Stroud, Abromovici et al. vorgeschlagen [SKCA96, SLA97, AS01, ASH+99, ASE04] und später von anderen Forschergruppen aufgegriffen und verbessert wurden [VDS04, SD06]. Die vorgestellten BIST-basierten Diagnose-Verfahren eignen sich insbesondere auch für die Erstellung einer Defect Map, wie sie für den Hard-Core basierten Ansatz benötigt wird. Im darauffolgenden Abschnitt werden Möglichkeiten für die Bereitstellung einer Defect Map für jedes defekte FPGA diskutiert.

#### 3.1 Fehlermodelle

Die Modellierung von möglichen Fehlern in den Verbindungsleitungen von FPGAs kann in der Regel an einem ausführlichen Modell erfolgen, da die Realisierung der

Verbindungen auf den FPGAs in den Handbüchern der FPGA-Hersteller dafür ausreichend beschrieben wird. Folgende Fehlermodelle finden üblicherweise Verwendung bei der Modellierung von Fehlern in den für die Verbindungen benötigten Komponenten [SWHA98]:

- Fehlermodelle für die programmierbaren Schalter (*Programmable connection switch | Programmable routing switch*, vgl. Abbildung 2.5 auf Seite 11) zwischen den Verbindungsleitungen

- Stuck-open / stuck-closed

- Fehlermodelle für die Verbindungsleitungen

- Stuck-at-0 / stuck-at-1

- Leitungsunterbrechung

- Brückenfehlermodell (bridging fault model)

Der Aufbau der Logikblöcke eines FPGAs wird von den führenden FPGA-Herstellern nur teilweise auf Gatter-Ebene beschrieben. Von den nicht auf Gatterebene beschriebenen Blöcken (zu denen z.B. die look-up table, Multiplexer, FlipFlops und weitere Bestandteile eines Logikblocks gehören) ist das Verhalten auf funktionaler Ebene jedoch in der Regel genau dokumentiert. Da jedes Fehlermodell eine Beschreibung der betrachteten Schaltung als Grundlage für die Beschreibung möglicher Defektauswirkungen verwendet, spiegelt sich das nicht vorhandene Gattermodell in den in der Literatur verwendeten Fehlermodellen für den Test und die Diagnose von FPGAs wider. Arbeiten, die speziell die Diagnose von Logikblöcken zum Ziel haben, verwenden daher oft ein funktionales Fehlermodell, das den Einfluss der Fehler in den Logikblöcken auf die Schaltung realisierungsunabhängig beschreibt. Die in Abbildung 2.5 als *connection block* zusammengefassten programmierbaren Schalter werden in vielen der angegebenen Ansätzen als zu dem Logikblock dazugehörig angesehen. Defekte in diesen Schaltern werden in diesem Fall als funktionale Fehler in den betroffenen Logikblöcken interpretiert.

Eine weitere Möglichkeit mit der nicht bekannten internen Struktur der Logikblöcke umzugehen, ist ein pseudo-vollständiger BIST (pseudo exhaustive test). Bei diesem Test wird jeder Ausgang eines Logikblocks getestet, indem alle möglichen 2<sup>n</sup> Kombinationen an die n Eingänge des Logikblocks angelegt werden, von denen der getestete Ausgang abhängt. Auch wenn durch das Testen mit allen möglichen Eingangskombinationen in der Regel mehr Kombinationen getestet werden als bei der Ermittlung einer optimalen Testmusterabdeckung, bietet diese Vorgehensweise den Vorteil, dass die erforderlichen Testmuster (=Eingangskombinationen) durch einfache Schaltungen auf dem FPGA generiert werden können und keine Modellierung des Logikblocks für die Ermittlung der Testmuster erforderlich ist. Durch den Vergleich der Ausgänge des getesteten Logikblocks mit den Ausgängen eines fehlerfreien Logikblocks können, bei

einem Durchlauf derselben Testmuster an den Eingängen der Logikblöcke, defekte Logikblöcke erkannt werden.

# 3.2 Diagnose über FPGA-BIST

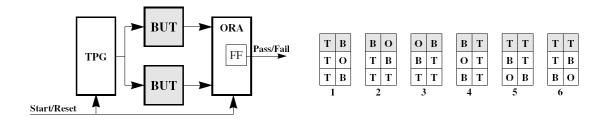

Stroud et. al schlagen in [SKCA96] ein BIST-Verfahren für den Test der Logikblöcke in FPGAs vor. Die schlechte Implementierbarkeit dieses Verfahrens aufgrund eines massiven Bedarfes an globalen Verbindungsleitungen auf dem FPGA wurde in [SLKA96] verbessert. Da die Test-Zeit durch das in [SLKA96] dargestellte Verfahren jedoch 33% mehr Zeit für die Durchführung des Tests benötigt, wird in [SLA97] eine Kombination der in [SKCA96] und [SLKA96] vorgeschlagenen Verfahren vorgestellt, die schließlich in [HGWS99] und zuletzt in [AS01] nochmals verbessert worden ist. Durch dieses Verfahren ist neben dem Test der Logikblöcke auch eine Lokalisierung von defekten Logikblöcken möglich. Im Folgenden soll der Ablauf dieser Diagnose kurz erläutert werden.

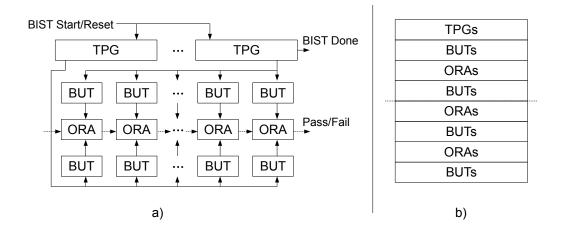

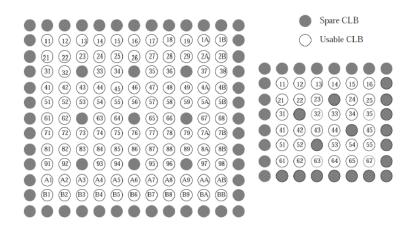

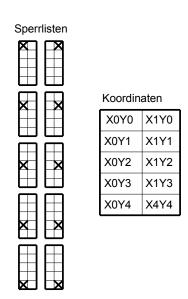

3.1 zeigt den Aufbau der verwendeten BIST-Architektur. Aus den Logikblöcken in der ersten Zeile des FPGAs werden Testmustergeneratoren (*test pattern generators* - TPGs) konfiguriert, die über globale Verbindungsleitungen Testmuster an die Eingänge der zu testenden Logikblöcke (*blocks under test* – BUTs) anlegen. Ab der dritten FPGA-Zeile werden in jeder zweiten Zeile Logikblöcke für den Vergleich der Antworten der BUTs auf die angelegten Testmuster konfiguriert (*output response analyzers* – ORAs). Durch Rekonfigurationen des FPGAs durch das ATE werden die BUTs in alle möglichen Betriebs-Modi gebracht und die Testmustergeneratoren jeweils so programmiert, dass alle für den jeweiligen Modus erforderlichen Testmuster – im folgenden als Testsequenz bezeichnet - an die BUTs angelegt werden. Für jeden Logikblock wird auf diese Weise ein vollständiger Test durchgeführt.

Nach jeder Rekonfiguration werden die folgenden Schritte ausgeführt:

- 1. Start der Test-Sequenz: Das ATE initialisiert TPGs, BUTs und ORAs und startet den Test (über BIST Start/Reset, siehe Abbildung 3.1)

- 2. Generierung der Testmuster durch die TPGs

- 3. Vergleich der Testantworten durch die ORAs.

- 4. Auslesen der Test-Ergebnisse aus dem FPGA (über Pass/Fail in Abbildung 3.1) durch das ATE.

Schritt 2 und 3 werden auf dem FPGA ohne Einwirkung von außen parallel für alle BUTs durchgeführt.

Abbildung 3.1: (a) Die BIST-Architektur aus [AS01] (b) Eine mögliche Zuordnung der Zeilen des zu testenden FPGAs

Die Bewertung der Testantworten erfolgt über einen Vergleich der BUTs, die jeweils oberhalb und unterhalb der ORAs liegen. Die ORAs können zum Auslesen der Test-Ergebnisse zu einem Shift-Register zusammengefasst werden.

Nachdem alle Betriebs-Modi der BUTs getestet wurden, werden die Zeilen des FPGAs entsprechend Abbildung 3.2 (b) umkonfiguriert, so dass in den darauffolgenden Tests die BUTs zu TPGs und ORAs werden und umgekehrt. Der Test ist beendet, wenn alle Logikblöcke des FPGAs als BUT in allen möglichen Betriebs-Modi getestet wurden. Alle Konfigurationen mit der Aufteilung entsprechend Abbildung 3.2 (a) und alle Konfigurationen mit der Aufteilung entsprechend Abbildung 3.2 (b) werden in [AS01] zusammengefasst jeweils als eine *test session* bezeichnet. Orientiert an der Richtung, in der die Testmuster zu den BUTs geleitet werden, wird *test session* (a) als NS und *test session* (b) als SN bezeichnet.

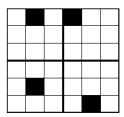

Eine Diagnose, also die Lokalisierung von defekten Logikblöcken, besteht aus der Abbildung einer nicht erwarteten Testantwort eines BUTs auf Fehler, die diese Testantwort erklären können. Durch die Anzahl der Shift-Operationen, die erforderlich sind bis das Ergebnis des fehlgeschlagenen Vergleiches am Pass/Fail-Ausgang anliegt, kann die Spalte festgestellt werden, in der ein Defekt aufgetreten ist. Auch die Bestimmung der Zeile ist möglich, da aus den Meldungen der ORAs Rückschlüsse auf die verursachende Zeile möglich sind. Abbildung 3.3 zeigt die möglichen Rückmeldungen für einen Fehler in der jeweils in der Tabelle in der ersten Spalte angegebenen Zeile für ein FPGA mit 8x8 Logikblöcken. Ein fehlerhafter Logikblock innerhalb eines ORAs oder eines TPGs muss nicht notwendigerweise dessen Funktion beeinträchtigen. Wenn wir jeweils die ORAs und TPGs als fehlerfrei annehmen (siehe Spalte "only BUT failures"), ist die Zuordnung des defekten Logikblocks zu einer Zeile einfach, da entweder in den inneren

| TPGs | BUTs |

|------|------|

| BUTs | ORAs |

| ORAs | BUTs |

| BUTs | ORAs |

| ORAs | BUTs |

| BUTs | ORAs |

| ORAs | BUTs |

| BUTs | TPGs |

| a)   | b)   |

Abbildung 3.2: Durch zwei verschiedene Zuordnungen der Zeilen wird jede Zeile des FPGA als BUT getestet [AS01]

Zeilen jeweils der ORA über und unter dem defekten Logikblock einen Defekt signalisiert, oder, in den äußeren Zeilen, durch die "Fail"-Meldung von nur einem ORA die Zeile bestimmt werden kann.

Erläuterung am Beispiel aus Abbildung 3.3: Ein defekter BUT in Zeile vier verursacht "Fail"-Meldungen von O3 und O5 in *test session* NS. Ein defekter BUT in Zeile eins verursacht eine "Fail"-Meldung in O2 in *test session* SN.

Auch dann, wenn man davon ausgeht, dass ORAs und TPGs von den defekten Logikblöcken betroffen sind, kann aus den Rückmeldungen der ORAs eindeutig auf die fehlerhafte Zeile geschlossen werden (siehe Spalte "with potiential ORA/TPG failures").

Erläuterung am Beispiel aus Abbildung 3.3: Wenn ein ORA fehlerhaft arbeitet, kann er einen Fehler melden, obwohl die verglichenen Ausgänge der BUTs übereinstimmen. Wenn in der *test session* NS in der zweiten Zeile ein Fehler vorliegt, kann dieser Fehler sich auch auf den in der *test session* SN an gleicher Stelle platzierten O2 auswirken, er wurde daher als potentieller Defekt in Klammern dort aufgeführt. Da wie in Abbildung 3.1 ersichtlich zwei TPGs in jeder test session vorhanden sind, würde sich ein Fehler in einem der TPGs so auswirken, dass alle ORAs eine "Fail"-Meldung liefern. Auch diese Fälle wurden für beide test sessions in Klammern in die Tabelle eingetragen. Auch mit der Berücksichtigung von Fehlern in den TPGs und ORAs ist die "Signatur" jeder Zeile der Tabelle eindeutig, d.h. es kann eindeutig auf die Zeile geschlossen werden, in der sich der defekte BUT befindet.

Auch die Diagnose von mehreren defekten Logikblöcken (*multiple faulty PLBs*) ist mit dem Ansatz möglich und wird ausführlich in [AS01] erläutert. Es gibt allerdings einige wenige Kombinationen, in denen die defekten Logikblöcke nicht lokalisiert werden

| Faulty | Function   | Function   | only BUT failures |                |                |                |                |                | with potential ORA/TPG failures |                |                |                |                |                |  |

|--------|------------|------------|-------------------|----------------|----------------|----------------|----------------|----------------|---------------------------------|----------------|----------------|----------------|----------------|----------------|--|

| Row    | Session NS | Session SN | Session NS        |                |                | Session SN     |                |                | Session NS                      |                |                | Session SN     |                |                |  |

|        |            |            | O <sub>3</sub>    | O <sub>5</sub> | O <sub>7</sub> | O <sub>2</sub> | O <sub>4</sub> | O <sub>6</sub> | O <sub>3</sub>                  | O <sub>5</sub> | O <sub>7</sub> | O <sub>2</sub> | O <sub>4</sub> | O <sub>6</sub> |  |

| 1      | TPG        | BUT        |                   |                |                | Х              |                |                | (X                              | Х              | X)             | Х              |                |                |  |

| 2      | BUT        | ORA        | Х                 |                |                |                |                |                | Х                               |                |                | (X)            |                |                |  |

| 3      | ORA        | BUT        |                   |                |                | Х              | Х              |                | (X)                             |                |                | Х              | Х              |                |  |

| 4      | BUT        | ORA        | Х                 | Х              |                |                |                |                | Х                               | Х              |                |                | (X)            |                |  |

| 5      | ORA        | BUT        |                   |                |                |                | Х              | Х              |                                 | (X)            |                |                | Х              | Х              |  |

| 6      | BUT        | ORA        |                   | Х              | Х              |                |                |                |                                 | Х              | Х              |                |                | (X)            |  |

| 7      | ORA        | BUT        |                   |                |                |                |                | Х              |                                 |                | (X)            |                |                | Х              |  |

| 8      | BUT        | TPG        |                   |                | Х              |                |                |                |                                 |                | Х              | (X             | Х              | X)             |  |

Abbildung 3.3: Die Rückmeldungen der ORAs bei einem fehlerhaften Logikblock [AS01]

können. In [AS01] heißt es dazu in der Zusammenfassung am Ende der Veröffentlichung:

"The multiple faulty PLBs that cannot be diagnosed appear to be very restrictive situations unlikely to occur in practice."

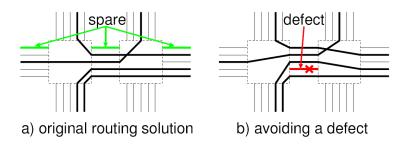

Eine Diagnose der Defekte in Routing-Ressourcen durch ein ähnliches Verfahren wurde in [SNLA02] beschrieben. Dieses Verfahren soll an dieser Stelle nicht betrachtet werden, da für den Hard-Core basierten Ansatz in der vorliegenden Form keine Diagnose der Routing-Ressourcen benötigt wird.

Neben der Diagnose durch ein Offline-BIST, d.h. der Diagnose eines FPGAs, bevor eine Schaltung auf dem FPGA implementiert wird, wurden auch Verfahren für ein Online-BIST vorgeschlagen. Ein Online-BIST geht davon aus, dass sich bereits eine Schaltung auf dem FPGA befindet und führt einen Test/eine Diagnose durch, ohne die Funktion

Abbildung 3.4: Zwei "self-testing areas" und deren Arbeitsweise [ASH+99]

der Schaltung zu beeinträchtigen. Dieses Vorgehen kann sinnvoll sein, wenn Defekte erst zur Laufzeit auf dem FPGA entstehen. Dies können z.B. Defekte auf dem FPGA sein, die bereits während der Herstellung des FPGAs entstanden sind und direkt nach der Herstellung noch kein Fehlverhalten des FPGAs verursacht haben, aber später zur Laufzeit durch Alterungseffekte auf dem FPGA als Defekt in Erscheinung treten. Vor allem in sicherheitskritischen Systemen ist daher ein BIST sinnvoll, um diese Defekte zur Laufzeit zu entdecken [SS99]. Das erste Verfahren für ein Online-BIST für FPGAs wurde 1998 von Shnidman et al. [SMSP98] vorgestellt. Dieses Verfahren erlaubt die Diagnose von defekten Logikblöcken für Bus-basierte FPGAs, also FPGAs, in denen Verbindungsleitungen vorhanden sind, welche die gesamte Höhe und die gesamte Breite des FPGAs umfassen. Das erste Online-BIST Verfahren, das auch für FPGAs mit segmentierten Verbindungsleitungen eingesetzt werden kann und auch eine Diagnose der Verbindungsleitungen ermöglicht, wurde 1999 von Stroud, Abromovici et al. [ASH+99, ASSE00] vorgestellt. Dieses Verfahren basiert auf der Idee von "self testing areas" (STARs), die über das FPGA bewegt werden, während die übrigen auf dem FPGA vorhandenen Logikblöcke weiterhin die Schaltung auf dem FPGA implementieren. Abbildung 3.4 skizziert eine vertikale und eine horizontale STAR, die horizontal, bzw. vertikal über das FPGA bewegt werden. Innerhalb der STARs findet ein Test statt, der vergleichbar mit dem bereits für den Offline-BIST vorgestellten Test verläuft.

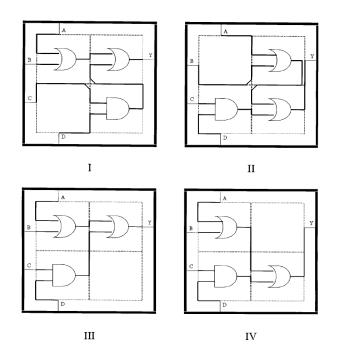

Die in der STAR enthaltenen Logikblöcke werden entsprechend Abbildung 3.5 in Bereiche unterteilt, die jeweils einen TPG (für die Implementierung eines TPG sind 3 Logikblöcke erforderlich), zwei BUT und einen ORA enthalten. Durch die abgebildeten sechs Konfigurationen für diesen Bereich ist gewährleistet, dass jeder der sechs Logikblöcke mindestens einmal die Rolle eines BUTs einnimmt. Nachdem in jeder der Konfigurationen alle Testmuster durch den TPG erzeugt wurden, wird der STAR einen Logikblock weiter geschoben. Wenn durch den ORA ein Fehler gemeldet wird, können entsprechend Abbildung 3.6 neue Aufteilungen für die Test-Konfigurationen gewählt werden, die eine eindeutige Identifizierung des defekten Logikblocks ermöglichen. Eine Weiterentwicklung dieses Ansatzes wurde von Verma et al. [VDS04] veröffentlicht.

Abbildung 3.5: Rotierende Konfigurationen für die Logikblöcke in einer STAR [ASH+99]

Abbildung 3.6: Neue Aufteilungen der Testbereiche zur Diagnose durch STARs [ASH+99]

Der Bereich, der den Tester enthält, wird hier als ROTE (ROving TEster) bezeichnet und es ist ein ROTE ausreichend, um einen defekten Logikblock zu lokalisieren. Dieses Verfahren für ein Online-BIST kann auch für ein Offline-BIST eingesetzt werden, indem der ROTE einmalig über das gesamte FPGA bewegt wird [VDS04].

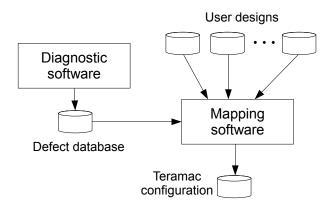

## 3.3 Erstellung und Bereitstellung einer Defect Map

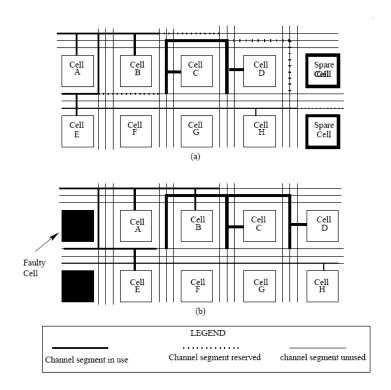

Viele der im Abschnitt "Vergleichbare Arbeiten" besprochenen Arbeiten basieren auf der Diagnose der defekten Komponenten in einem defekten FPGA. Mishra und Goldstein skizzieren die Idee einer Defect Map, die auch eine Voraussetzung für das hier vorgestellte Hard-Core basierte Verfahren ist [MG03]: